I chiplet stanno guadagnando rinnovata attenzione nel mercato automobilistico, dove la crescente elettrificazione e la forte concorrenza stanno costringendo le aziende ad accelerare i propri programmi di progettazione e produzione.

L’elettrificazione ha acceso il fuoco in alcune delle case automobilistiche più grandi e conosciute, che stanno lottando per rimanere competitive a fronte di finestre di mercato molto brevi e requisiti in continua evoluzione. A differenza del passato, quando le case automobilistiche generalmente eseguivano cicli di progettazione da cinque a sette anni, la tecnologia più recente nei veicoli di oggi potrebbe essere considerata superata nel giro di diversi anni. E se non riescono a tenere il passo, c’è un intero nuovo gruppo di startup che producono veicoli economici con la possibilità di aggiornare o modificare le funzionalità con la stessa rapidità di un aggiornamento del software.

Ma il software presenta limiti in termini di velocità, sicurezza e affidabilità e la possibilità di personalizzare l’hardware è l’obiettivo su cui molte case automobilistiche stanno ora impegnandosi. È qui che si inseriscono i chiplet e l’attenzione ora è su come costruire un’interoperabilità sufficiente tra ecosistemi di grandi dimensioni per renderlo un mercato plug-and-play. I fattori chiave per consentire l’interoperabilità dei chiplet automobilistici includono la standardizzazione, le tecnologie di interconnessione, i protocolli di comunicazione, la gestione energetica e termica, la sicurezza, i test e la collaborazione dell’ecosistema.

Analogamente alle applicazioni non automobilistiche a livello di consiglio di amministrazione, molti sforzi di progettazione si stanno concentrando su un approccio die-to-die, che sta portando a una serie di nuove considerazioni e compromessi di progettazione. A livello di chip, le interconnessioni tra vari processori, chip, memoria e I/O stanno diventando più complesse a causa dei maggiori requisiti di prestazioni di progettazione, stimolando una raffica di attività relative agli standard. Sono stati proposti diversi tipi di interconnessione e interfaccia per servire a scopi diversi, mentre emergono chiplet le tecnologie per funzioni dedicate – processori, memorie e I/O, solo per citarne alcuni – stanno cambiando l’approccio alla progettazione dei chip.

"Gli OEM automobilistici si stanno rendendo conto che, per controllare il proprio destino, dovranno controllare i propri SoC", ha affermato David Fritz, vicepresidente dei sistemi virtuali e ibridi presso Siemens EDA. “Tuttavia, non capiscono quanta strada abbia fatto l’EDA da quando erano al college nel 1982. Inoltre, credono di dover passare all’ultimo nodo del processo, dove un set di maschere costerà 100 milioni di dollari. Non possono permetterselo. Inoltre non hanno accesso ai talenti perché il pool di talenti è piuttosto piccolo. Tutto questo insieme arriva alla consapevolezza da parte degli OEM che per controllare il proprio destino, hanno bisogno di una tecnologia sviluppata da altri, ma che può essere combinata, tuttavia, necessaria per avere un prodotto unico e differenziato che sono sicuri sia a prova di futuro almeno per pochi anni modello. Allora diventa economicamente sostenibile. L’unica cosa che va bene sono i chiplet.”

I chiplet possono essere ottimizzati per funzioni specifiche, che possono aiutare le case automobilistiche a soddisfare i requisiti di affidabilità, sicurezza e protezione con una tecnologia collaudata su più progetti di veicoli. Inoltre, possono abbreviare il time-to-market e, in ultima analisi, ridurre il costo di diverse caratteristiche e funzioni.

La domanda di chip è in aumento negli ultimi dieci anni. Secondo Allied Market Research, la domanda globale di chip automobilistici crescerà da 49.8 miliardi di dollari nel 2021 a 121.3 miliardi di dollari entro il 2031. Questa crescita attirerà ancora più innovazione e investimenti nel settore dei chip automobilistici, e si prevede che i chiplet saranno i grandi beneficiari.

Ma il mercato dei chiplet avrà bisogno di tempo per maturare e probabilmente verrà implementato in più fasi. Inizialmente, un fornitore fornirà diversi tipi di stampi proprietari. Quindi, i partner lavoreranno insieme per fornire chiplet per supportarsi a vicenda, come è già accaduto con alcuni fornitori. La fase finale sarà costituita da chiplet universalmente interoperabili, supportati da UCIe o da qualche altro schema di interconnessione.

Arrivare alla fase finale sarà la più difficile e richiederà cambiamenti significativi. Per garantire l’interoperabilità, è necessario che porzioni sufficientemente ampie dell’ecosistema automobilistico e della catena di fornitura si uniscano, inclusi sviluppatori di hardware e software, fonderie, OSAT e fornitori di materiali e apparecchiature.

Lo slancio sta crescendo

Il lato positivo è che non tutto parte da zero. A livello di scheda, moduli e sottosistemi hanno sempre utilizzato interfacce chip-to-chip integrate e continueranno a farlo. Vari fornitori di chip e IP, tra cui Cadence, Diode, Microchip, NXP, Renesas, Rambus, Infineon, Arm e Synopsys, forniscono chip di interfaccia o IP standard per creare il silicio di interfaccia.

Il Consorzio Universal Chiplet Interconnect Express (UCIe). è la forza trainante dietro lo standard di interconnessione aperto die-to-die. Il gruppo ha rilasciato la sua ultima specifica UCIe 1.1 nell'agosto 2023. I membri del consiglio includono Alibaba, AMD, Arm, ASE, Google Cloud, Intel, Meta, Microsoft, NVIDIA, Qualcomm e Samsung e altri. I partner del settore stanno mostrando un ampio sostegno. Sono stati proposti anche AIB e Bunch of Wires (BoW). Inoltre, Arm ha appena rilasciato la propria architettura di sistema chiplet, insieme a una specifica AMBA aggiornata per standardizzare i protocolli per i chiplet.

“I chiplet sono già qui, spinti dalla necessità”, ha affermato Arif Khan, direttore senior del gruppo marketing di prodotto per la progettazione IP presso Cadence. “Le crescenti dimensioni dei processori e dei SoC stanno raggiungendo il limite del reticolo e le diseconomie di scala. I guadagni incrementali derivanti dai progressi tecnologici di processo sono inferiori all’aumento dei costi per transistor e progettazione. I progressi nella tecnologia di packaging (2.5D/3D) e la standardizzazione dell’interfaccia a livello die-to-die, come UCIe, faciliteranno lo sviluppo dei chiplet”.

Quasi tutti i chiplet utilizzati oggi sono sviluppati internamente da grandi produttori di chip come Intel, AMD e Marvell, perché possono controllare strettamente le caratteristiche e il comportamento di tali chiplet. Ma si sta lavorando a tutti i livelli per aprire questo mercato a più operatori. Quando ciò accadrà, le aziende più piccole potranno iniziare a trarre vantaggio da ciò che i pionieri di alto profilo hanno realizzato finora e a innovare attorno a tali sviluppi.

"Molti di noi credono che il sogno di avere un portafoglio di chiplet standard e interoperabili richiederà probabilmente anni prima di diventare realtà", ha affermato Guillaume Boillet, direttore senior del marketing strategico di Arteris, aggiungendo che l'interoperabilità emergerà da gruppi di partner che stanno affrontando il rischio di specifiche incomplete.

Ciò sta anche aumentando l’attrattiva degli FPGA e degli eFPGA, che possono fornire un livello di personalizzazione e aggiornamenti per l’hardware sul campo. "I chiplet sono una cosa reale", ha affermato Geoff Tate, CEO di Flex Logix. “Al momento, un’azienda che costruisce due o più chiplet può operare in modo molto più economico di un’azienda che costruisce uno stampo quasi delle dimensioni di un reticolo con un rendimento quasi nullo. La standardizzazione dei chiplet sembra essere ancora lontana. Anche l’UCIe non è ancora uno standard fisso. Non tutti sono d'accordo su UCIe, test bare die e chi possiede il problema quando il pacchetto integrato non funziona, ecc. Abbiamo alcuni clienti che utilizzano o stanno valutando eFPGA per interfacce in cui gli standard sono in continuo cambiamento come UCIe. Possono implementare il silicio adesso e utilizzare l’eFPGA per conformarsi alle modifiche degli standard in un secondo momento”.

Ci sono anche altri sforzi a supporto dei chiplet, anche se per ragioni leggermente diverse, in particolare il costo crescente del ridimensionamento dei dispositivi e la necessità di incorporare più funzionalità nei chip, che sono vincolati dal reticolo nei nodi più avanzati. Ma questi sforzi aprono anche la strada ai chiplet nel settore automobilistico, e c’è un forte sostegno da parte dell’industria per far sì che tutto questo funzioni. Ad esempio, sotto il patrocinio di SEMI, ASME e tre società IEEE, la nuova Heterogeneous Integration Roadmap (HIR) esamina vari problemi di progettazione, materiali e imballaggio della microelettronica per elaborare una tabella di marcia per l’industria dei semiconduttori. Il loro focus attuale include 2.5D, 3D-IC, packaging a livello di wafer, fotonica integrata, MEMS e sensori e system-in-package (SiP), aerospaziale, automobilistico e altro ancora.

Al recente Heterogeneous Integration Global Summit 2023, rappresentanti di AMD, Applied Materials, ASE, Lam Research, MediaTek, Micron, Onto Innovation, TSMCe altri hanno dimostrato un forte supporto per i chiplet. Un altro gruppo che supporta i chiplet è il Scambio di progettazione di chiplet (CDX), che fa parte del Architettura aperta specifica del dominio (ODSA) e la Open Compute Project Foundation (OCP). La carta Chiplet Design Exchange (CDX) si concentra sulle varie caratteristiche del chiplet e dell'integrazione dei chiplet, inclusi gli standard di scambio di progettazione elettrica, meccanica e termica dei circuiti 2.5D impilati e dei circuiti integrati 3D (IC 3D). I suoi rappresentanti includono Ansis, Materiali applicati, Arm, Ayar Labs, Broadcom, Cadence, Intel, Macom, Marvell, Microsemi, NXP, Siemens EDA, Synopsys e altri.

"Ciò che le aziende automobilistiche desiderano in termini di funzionalità di ciascun chiplet è ancora in fase di sconvolgimento", ha osservato Fritz di Siemens. “Un estremo ha questi problemi, l’altro estremo ha quegli stessi problemi. Questo è il punto debole. Questo è ciò che serve. E questi sono i tipi di aziende che possono andare avanti e fare quel tipo di lavoro, e poi potresti metterle insieme. Quindi questa cosa dell'interoperabilità non è un grosso problema. L'OEM può rendere il tutto troppo complesso dicendo: "Devo gestire l'intero spettro di possibilità". L'alternativa è che potrebbero dire: "È proprio come un PCIe ad alta velocità". Se voglio comunicare dall'uno all'altro, so già come farlo. Ho dei driver che eseguono il mio sistema operativo. Ciò risolverebbe un sacco di problemi, ed è lì che credo che andrà a finire.

Un percorso verso lo sviluppo di chiplet universali?

Andando avanti, i chiplet sono un punto focale sia per l’industria automobilistica che per quella dei chip, e ciò coinvolgerà tutto, dall’IP dei chiplet alle interconnessioni di memoria, alle opzioni e limitazioni di personalizzazione.

Ad esempio, Renesas Electronics ha annunciato nel novembre 2023 i piani per i suoi SoC e MCU di prossima generazione. L'azienda si rivolge a tutte le principali applicazioni nel dominio digitale automobilistico, comprese informazioni anticipate sul suo SoC R-Car di quinta generazione per applicazioni ad alte prestazioni con tecnologia avanzata di integrazione chiplet in-package, che hanno lo scopo di fornire agli ingegneri automobilistici una maggiore flessibilità di personalizzazione i loro disegni.

Renesas ha osservato che se saranno necessarie maggiori prestazioni dell’IA nei sistemi avanzati di assistenza alla guida (ADAS), gli ingegneri avranno la capacità di integrare gli acceleratori AI in un singolo chip. La società ha affermato che questa tabella di marcia arriva dopo anni di collaborazione e discussioni con i clienti Tier 1 e OEM, che chiedono a gran voce un modo per accelerare lo sviluppo senza compromettere la qualità, inclusa la progettazione e la verifica del software ancor prima che l'hardware sia disponibile.

“A causa della necessità sempre crescente di aumentare il calcolo su richiesta e della crescente necessità di livelli più elevati di autonomia nelle auto di domani, vediamo sfide nelle soluzioni monolitiche che si adattano e soddisfano le esigenze prestazionali del mercato nei prossimi anni”, ha affermato Vasanth Waran, direttore senior per SoC Business & Strategies presso Renesas. “I chiplet consentono alle soluzioni di elaborazione di scalare ben oltre le esigenze del mercato”.

Renesas ha annunciato l'intenzione di creare a famiglia di prodotti basati su chiplet specificamente rivolto al mercato automobilistico a partire dal 2025.

Le interfacce standard consentono la personalizzazione del SoC

Non è del tutto chiaro quanta sovrapposizione ci sarà tra i processori standard, che è il luogo in cui oggi viene utilizzata la maggior parte dei chiplet, e i chiplet sviluppati per applicazioni automobilistiche. Ma le tecnologie e gli sviluppi sottostanti certamente si rafforzeranno a vicenda man mano che questa tecnologia si sposterà verso nuovi mercati.

“Che si tratti di un acceleratore AI o di un’applicazione automobilistica ADAS, i clienti necessitano di blocchi IP di interfaccia standard”, ha osservato David Ridgeway, senior product manager, gruppo di soluzioni accelerate IP presso Synopsys. “È importante fornire sottosistemi IP completamente verificati in base ai requisiti di personalizzazione IP per supportare i componenti del sottosistema utilizzati nei SoC dei clienti. Quando dico personalizzazione, potresti non renderti conto di quanto sia diventato personalizzabile l'IP nel corso degli ultimi 10-20 anni, sia dal lato PHY che dal lato controller. Ad esempio, PCI Express è passato da PCIe Gen 3 a Gen 4 a Gen 5 e ora Gen 6. Il controller può essere configurato per supportare più modalità di biforcazione con larghezze di collegamento inferiori, tra cui un x16, due x8 o quattro x4. Il nostro team IP del sottosistema collabora con i clienti per garantire che tutti i requisiti di personalizzazione siano soddisfatti. Per le applicazioni IA, l'integrità del segnale e dell'alimentazione è estremamente importante per soddisfare i requisiti prestazionali. Quasi tutti i nostri clienti cercano di spingersi oltre per raggiungere la massima velocità di larghezza di banda della memoria possibile, in modo che la loro TPU possa elaborare molte più transazioni al secondo. Ogni volta che le applicazioni riguardano il cloud computing o l’intelligenza artificiale, i clienti desiderano il tasso di risposta più rapido possibile”.

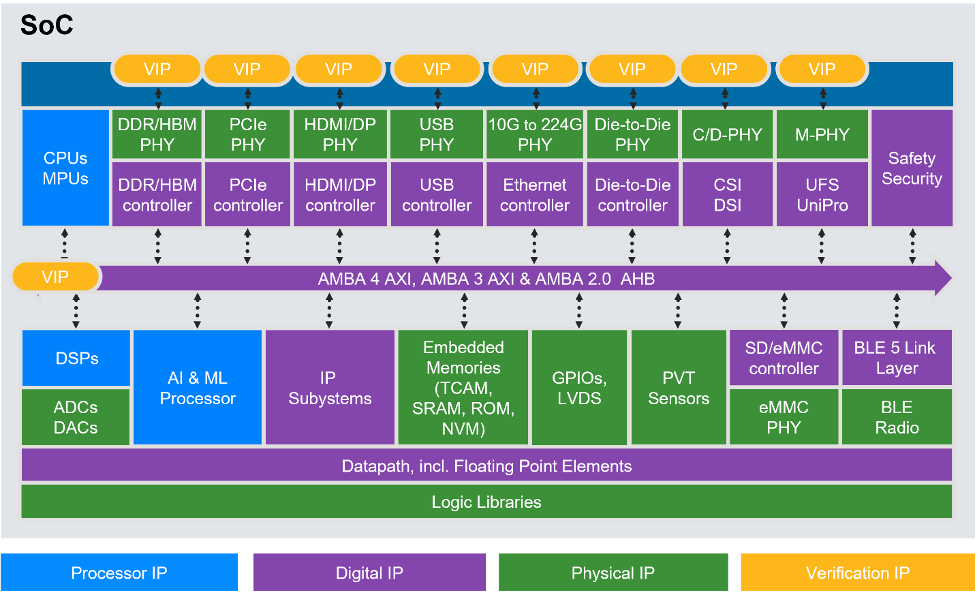

Fig 1: I blocchi IP che includono processore, digitale, PHY e verifica aiutano gli sviluppatori a implementare l'intero SoC. Fonte: sinossi

L’ottimizzazione del PPA ha l’obiettivo finale di aumentare l’efficienza e questo rende i chiplet particolarmente attraenti nelle applicazioni automobilistiche. Quando l’UCIe maturerà, si prevede che migliorerà esponenzialmente le prestazioni complessive. Ad esempio, UCIe può fornire una larghezza di banda costiera da 28 a 224 GB/s/mm in un pacchetto standard e da 165 a 1317 GB/s/mm in un pacchetto avanzato. Ciò rappresenta un miglioramento delle prestazioni da 20 a 100 volte. Ridurre la latenza da 20 ns a 2 ns rappresenta un miglioramento di 10 volte. Un altro vantaggio è un'efficienza energetica circa 10 volte maggiore, a 0.5 pJ/b (pacchetto standard) e 0.25 pJ/b (pacchetto avanzato). La chiave è accorciare la distanza dell’interfaccia quando possibile.

Per ottimizzare la progettazione dei chiplet, il Consorzio UCIe fornisce alcuni suggerimenti:

- Attenta considerazione della pianificazione delle linee di demarcazione dell'architettura (ovvero i confini dei chiplet), ottimizzazione di potenza, latenza, area di silicio e riutilizzo IP. Ad esempio, la personalizzazione di un chiplet che necessita di un nodo di processo all'avanguardia e il riutilizzo di altri chiplet su nodi più vecchi può avere un impatto su costi e tempi.

- È necessario pianificare i vincoli termici e meccanici dell'imballaggio per gli involucri termici, i punti caldi, il posizionamento dei chiplet e l'instradamento e i breakout degli I/O.

- I nodi del processo devono essere selezionati con attenzione, in particolare nel contesto dello schema di erogazione di energia associato.

- La strategia di test per i chiplet e le parti confezionate/assemblate deve essere sviluppata in anticipo per garantire che i problemi del silicio vengano rilevati nella fase di test a livello di chiplet anziché dopo l'assemblaggio in un pacchetto.

Conclusione

L’idea di standardizzare le interfacce die-to-die sta prendendo piede rapidamente, ma il percorso per arrivarci richiederà tempo, impegno e molta collaborazione tra aziende che raramente comunicano tra loro. Costruire un veicolo richiede una determinata casa automobilistica. Costruire un veicolo con chiplet richiede la collaborazione di un intero ecosistema che includa sviluppatori, fonderie, OSAT e fornitori di materiali e attrezzature.

Gli OEM automobilistici sono esperti nel mettere insieme i sistemi e nel trovare modi innovativi per ridurre i costi. Ma resta da vedere quanto velocemente ed efficacemente potranno costruire e sfruttare un ecosistema di chiplet interoperabili per ridurre i cicli di progettazione, migliorare la personalizzazione e adattarsi a un mondo in cui la tecnologia all’avanguardia potrebbe essere obsoleta nel momento in cui sarà completamente progettata e testata. e a disposizione dei consumatori.

— Ann Mutschler ha contribuito a questo rapporto.

- Distribuzione di contenuti basati su SEO e PR. Ricevi amplificazione oggi.

- PlatoData.Network Generativo verticale Ai. Potenzia te stesso. Accedi qui.

- PlatoAiStream. Intelligenza Web3. Conoscenza amplificata. Accedi qui.

- PlatoneESG. Carbonio, Tecnologia pulita, Energia, Ambiente, Solare, Gestione dei rifiuti. Accedi qui.

- Platone Salute. Intelligence sulle biotecnologie e sulle sperimentazioni cliniche. Accedi qui.

- Fonte: https://semiengineering.com/why-chiplets-are-so-critical-in-automotive/