Selama GOMACTech konferensi yang diadakan di Carolina Selatan minggu lalu Saya melakukan panggilan Zoom dengan Deepak Shankar, Pendiri dan VP Teknologi di Mirabilis Design Inc. untuk mengajukan pertanyaan dan melihat demo langsung VisualSim – platform pemodelan, simulasi, eksplorasi, dan kolaboratif untuk mengembangkan elektronik dan SoC. Apa yang membuat VisualSim begitu istimewa adalah ia dibundel dengan sekitar 500 blok IP tingkat tinggi yang siap digunakan, termasuk 35 prosesor ARM, sekitar 100 prosesor, dan lebih dari 30 interkoneksi berbeda. Pengguna VisualSim dengan cepat menghubungkan blok IP ini bersama-sama secara visual untuk membuat sistem mereka, lengkap dengan jaringan. Seorang desainer otomotif dapat memodelkan seluruh jaringan, termasuk komunikasi 5G, Ethernet, SDA, dan pembaruan OTA dengan VisualSim.

Model tingkat tinggi memungkinkan eksplorasi arsitektur tercepat dan melakukan pertukaran arsitektur, jauh sebelum implementasi dimulai dengan kode RTL. Anda dapat memodelkan aktivitas kompleks seperti bus, memori, dan bahkan cache, mengukur hal-hal seperti penundaan dan latensi end-to-end. Insinyur dapat mengukur rasio cache hit/miss, dan apa yang terjadi dengan permintaan ke cache L2. Semua protokol jaringan populer dimodelkan: AXI, CHI, CMN600, Arteris NOC, UCIe, dll.

Dengan pendekatan pemodelan ini, seorang arsitek dapat memodelkan SoC, melengkapi sistem pesawat terbang atau otomotif, dan kemudian mulai mengukur kinerjanya untuk melihat apakah memenuhi persyaratan. VisualSim adalah simulator multi-domain yang dapat mengintegrasikan analog, perangkat lunak, sistem tenaga, digital dan jaringan ke dalam satu model.

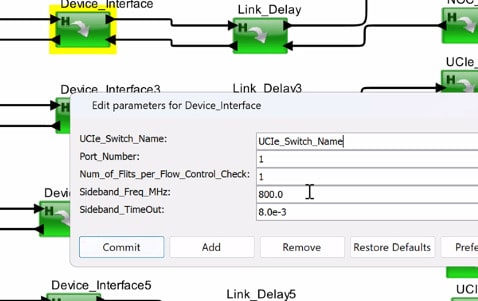

Untuk demo langsung, Deepak menunjukkan kepada saya desain berbasis chiplet yang memiliki chiplet terpisah untuk DSP, GPU, prosesor AI, dan CPU yang semuanya terhubung bersama menggunakan UCIe, dan setiap blok IP diberi parameter untuk memungkinkan penyesuaian dan eksplorasi.

Mendorong ke dalam blok UCIe ada IP yang disebut saklar UCIe, dan pengguna dapat menyesuaikan blok ini dengan lima parameter, semuanya pada tingkat tinggi.

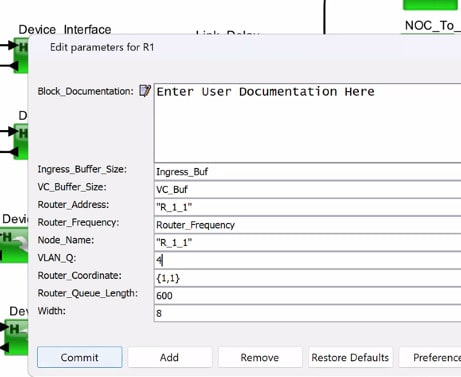

Blok IP router memiliki 10 parameter untuk penyesuaian.

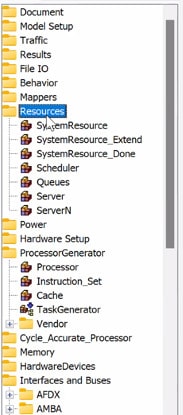

Untuk menemukan setiap blok IP ada daftar yang dapat digulir di sisi kiri GUI, dengan setiap kelompok IP di perpustakaan. Dalam hitungan detik Anda dapat menelusuri, memilih, dan mulai menyesuaikan IP.

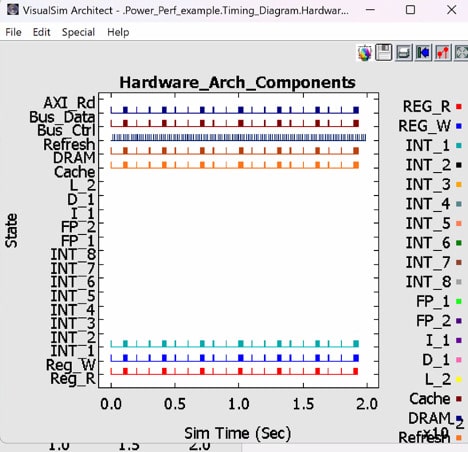

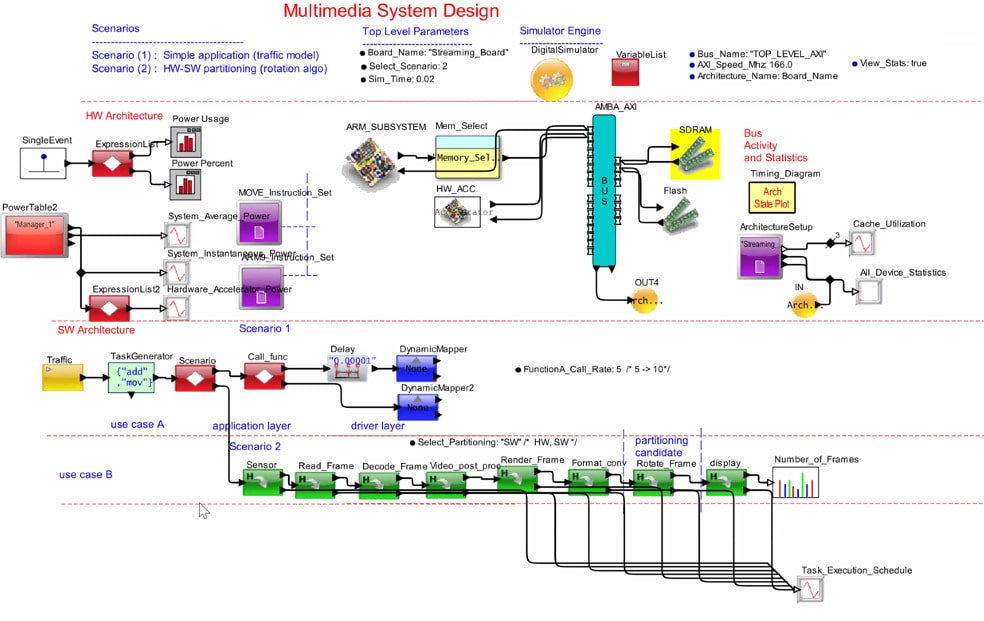

Di VisualSim Anda menghubungkan setiap IP dalam aliran data, tetap pada level tinggi. Demo langsung berikutnya adalah untuk desain sistem multimedia, dan untuk mensimulasikan 20 ms memerlukan waktu dinding sekitar 15 detik, dijalankan pada laptop. Saat simulasi berjalan, Anda dapat melihat kinerja sistem sebagai daya sesaat, mengukur pemanfaatan saluran pipa, pemanfaatan cache, penggunaan memori, dan bahkan melihat diagram waktu. Simulasi waktu nyata ini memicu 7.5 juta peristiwa, dan pelanggan membuat model ini dalam waktu kurang dari 2 minggu, termasuk seluruh SoC.

Contoh pelanggan lain yang disebutkan Deepak mencakup 45 master dan diselesaikan dalam waktu sekitar 4 minggu, telah diuji sepenuhnya.

Anda dapat melihat ke dalam blok IP mana pun dan menganalisis metrik seperti lulus/gagal, lalu memahami mengapa blok tersebut gagal. Bahkan terdapat mesin AI untuk membantu menganalisis data dengan lebih efisien, seperti menemukan buffer overflow yang menyebabkan kegagalan. Saat model Anda berjalan, ada analitik yang diambil untuk membantu mengukur kinerja sistem dan mengidentifikasi hambatan arsitektur.

VisualSim diperbarui dua kali setahun, dan kemudian ada pembaruan patch ketika blok IP baru ditambahkan. Seorang arsitek mendefinisikan persyaratan dalam file Excel, dengan metrik seperti batas latensi dan hunian buffer.

Pengguna VisualSim dapat menentukan kisaran ukuran muatan dalam byte, rentang kecepatan, dan nilai yang diinginkan. Model sistem Anda dapat menelusuri kombinasi untuk menemukan kumpulan parameter terbaik. Simulator bahkan memahami cara menjelajahi nilai min, maks, dan pilihan. Anda dapat menentukan parameter sistem mana yang akan dieksplorasi. Demo sistem multimedia ditampilkan berikutnya dan kemudian disimulasikan secara langsung.

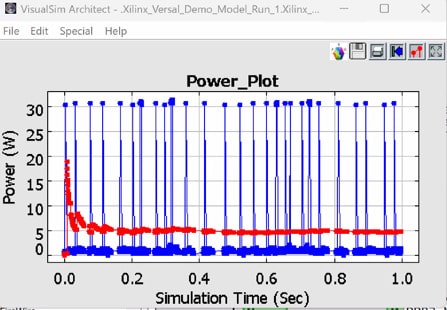

Untuk blok FPGA Anda memilih vendor dan nomor komponen, lalu Anda dapat melihat latensi untuk setiap Tugas dan statistik saluran NOC setelah simulasi dijalankan. Plot daya ditampilkan selama 1 detik operasi saat menggunakan bagian Xilinx Versal.

Semua demo langsung dijalankan di laptop Windows. OS lain yang didukung adalah: Unix, Mac. Menjalankan VisualSim memerlukan infrastruktur HW minimal, karena modelnya tingkat tinggi.

Pengguna VisualSim menerima lebih dari 500 contoh yang dibuat sebelumnya untuk membantu Anda memulai dengan cepat, seperti sistem komunikasi lengkap dengan Antena, Transceiver, FPGA dengan baseband, dan antarmuka Ethernet. Arsitek sistem yang menggunakan VisualSim dapat berkolaborasi dengan semua spesialis tingkat rendah, seperti desainer RTL.

Pertukaran tingkat sistem dapat dimodelkan dan dievaluasi, seperti:

- Mengubah dari modulasi 64-QAM ke QPSK

- Prosesor lebih cepat ke lebih lambat

- Mengubah spesifikasi Ethernet

Jika Anda memulai dengan VisualSim untuk memodelkan, mengimplementasikan, lalu mengukur, Anda akan melihat akurasi 95% dibandingkan dengan hasil implementasi RTL. Tujuan dari penggunaan model tingkat tinggi adalah untuk menghilangkan masalah kinerja sebelum implementasi atau integrasi. Sebenarnya tidak diperlukan pengkodean untuk keseluruhan model sistem.

Mirabilis memiliki 65 pelanggan di seluruh dunia sejauh ini dan sekitar 250 proyek telah selesai. Beberapa klien terkenal antara lain: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Kesimpulan

Di masa lalu, seorang perancang sistem mungkin menuangkan idenya di atas serbet saat makan di restoran, lalu kembali bekerja dan menyusun beberapa spreadsheet Excel dengan persamaan misterius untuk membuat model. Saat ini ada pilihan baru, dan itu adalah memberi VisualSim dari Mirabilis cobalah. Anda sekarang dapat memodelkan keseluruhan sistem hanya dalam beberapa minggu, bersamaan dengan melakukan trade-off arsitektural sambil menjalankan simulasi sebenarnya, semuanya sebelum masuk ke detail implementasi yang mendetail.

Blog terkait

Bagikan postingan ini melalui:

- Konten Bertenaga SEO & Distribusi PR. Dapatkan Amplifikasi Hari Ini.

- PlatoData.Jaringan Vertikal Generatif Ai. Berdayakan Diri Anda. Akses Di Sini.

- PlatoAiStream. Intelijen Web3. Pengetahuan Diperkuat. Akses Di Sini.

- PlatoESG. Karbon, teknologi bersih, energi, Lingkungan Hidup, Tenaga surya, Penanganan limbah. Akses Di Sini.

- PlatoHealth. Kecerdasan Uji Coba Biotek dan Klinis. Akses Di Sini.

- Sumber: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/