La résistance de grille MOSFET est un paramètre très important, déterminant de nombreuses caractéristiques des circuits MOSFET et CMOS, telles que :

• Vitesse de commutation

• Délai RC

• Fmax - fréquence maximale des oscillations

• Bruit de porte (thermique)

• Résistance série et facteur de qualité dans les condensateurs MOS et les varactors

• Vitesse de commutation et uniformité dans les FET de puissance

• De nombreuses autres caractéristiques d'appareils et de circuits

De nombreux articles universitaires et de recherche ont été écrits sur la résistance de porte. Cependant, pour le travail pratique des concepteurs de circuits intégrés et des ingénieurs de mise en page, de nombreuses choses importantes n'ont pas été discutées ou expliquées, par exemple :

• La résistance de grille est-elle gérée par des modèles SPICE ou par des outils d'extraction parasites ?

• Comment les outils d'extraction parasite gèrent-ils la résistance de grille ?

• Comment évaluer la résistance de grille à partir du layout ou de la netlist extraite après le layout ?

• Comment déterminer si la résistance de grille est limitée par la résistance de grille « intrinsèque » (gate poly), ou par le routage de la métallisation de grille, et quels sont les couches et les polygones les plus critiques ?

• Est-ce que l'effet de grille distribué (facteurs de 1/3 et 1/12, pour les polycontacts simples et doubles) est capturé dans le flux de conception du circuit intégré (dans PDK) ?

• La composante de résistance de grille verticale est-elle capturée dans les PDK de fonderie ?

• Le portail doit-il être plus large ou plus étroit pour réduire la résistance du portail ?

• Quelle est la différence entre la gestion de la résistance de grille dans les PDK pour RF par rapport aux MOSFET ou aux cellules p classiques ?

Le but de cet article est de démystifier ces questions et de fournir des informations aux ingénieurs de conception et de mise en page de circuits intégrés afin de mieux comprendre la résistance de grille dans leurs conceptions.

Définition et mesure de la résistance de grille

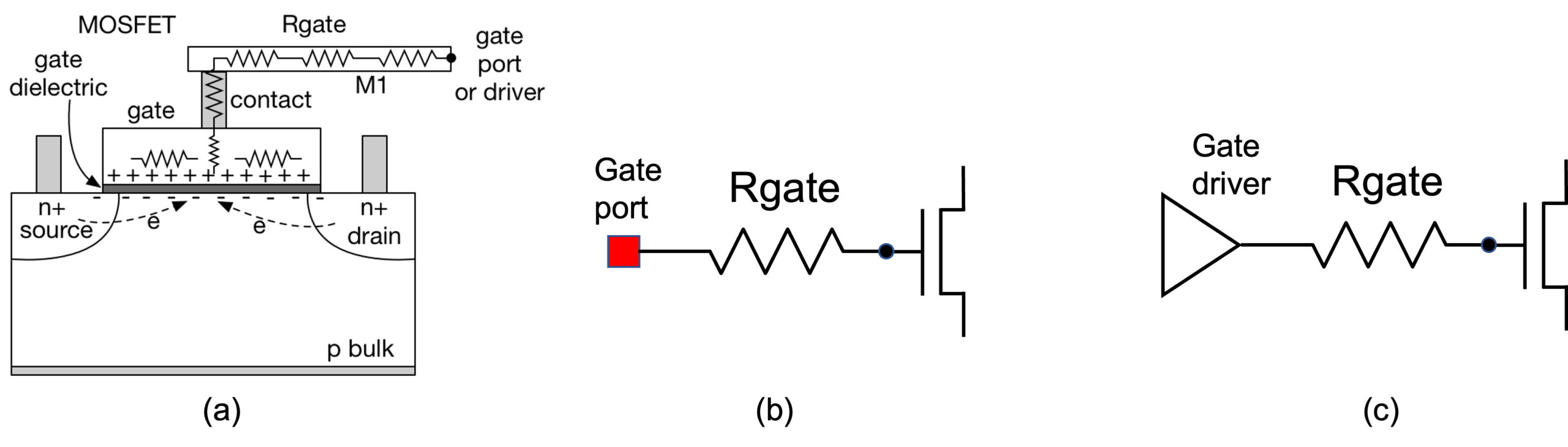

La résistance de grille est une résistance "efficace" du point d'entraînement (port de grille ou pilote de grille) à la ou aux broches d'instance de grille MOSFET - voir Fig.1. (la broche d'instance est un point de connexion entre une borne du modèle SPICE et un réseau résistif un réseau).

Cependant, la simplicité du schéma de la figure 1 peut être très trompeuse. Les réseaux de portes peuvent être de très grande taille, contenir de nombreux points de conduite, de nombreuses (dizaines de) couches (métal et via), des millions de polygones et jusqu'à des millions de broches d'instance de porte (points de connexion pour les terminaux de porte du modèle SPICE) - voir Figure 2.

Le réseau de portes forme un grand système distribué, avec un ou plusieurs points de conduite et de nombreux points de destination.

Très souvent, le réseau de grille ressemble et se comporte comme un énorme réseau d'horloge régulier, distribuant la tension de grille à un FET.

Déduire une résistance de grille équivalente et efficace pour un système aussi vaste et complexe n'est pas une tâche simple et directe. La simulation de circuit SPICE ne signale pas explicitement la valeur de résistance de grille.

Connaître la valeur de la résistance de grille est très utile pour estimer la vitesse de commutation, le retard, le bruit, Fmax et d'autres caractéristiques, pour voir si les caractéristiques sont conformes aux spécifications. De plus, connaître les contributions à la résistance de grille - par couche et par polygones de disposition - est très utile pour guider les efforts d'optimisation de la disposition.

Gestion de la résistance de grille par des outils d'extraction parasites

Pour comprendre la résistance de grille dans le flux de conception de circuits intégrés, il est important de savoir comment les outils d'extraction parasites la traitent et la modélisent.

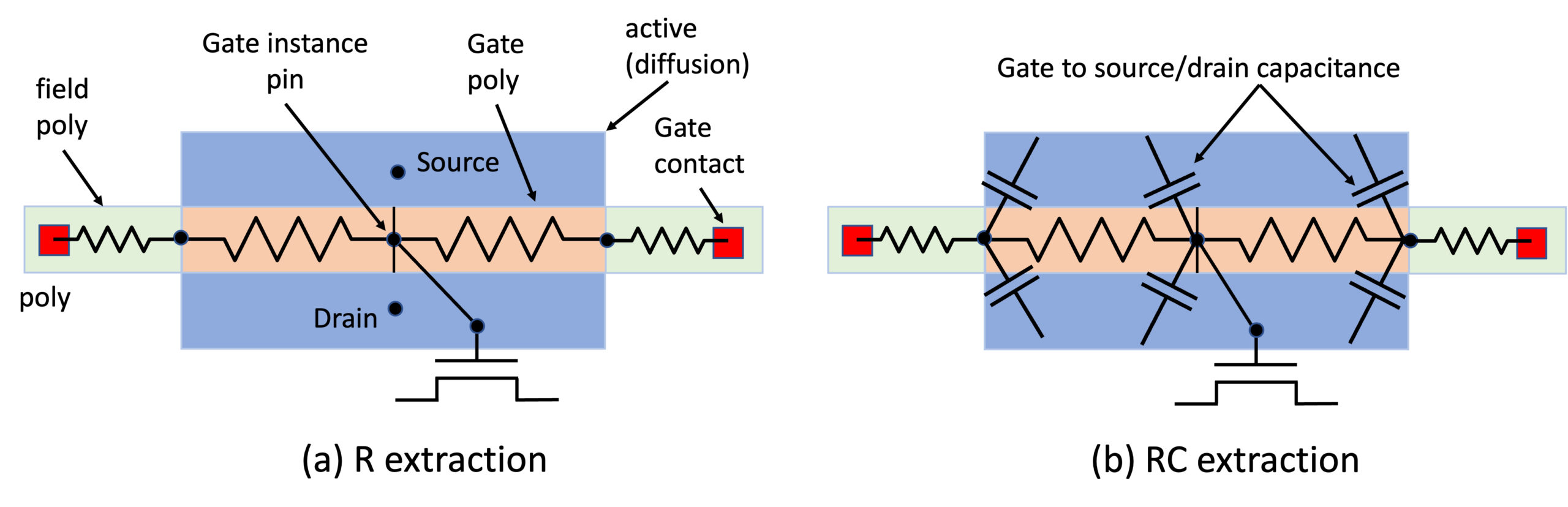

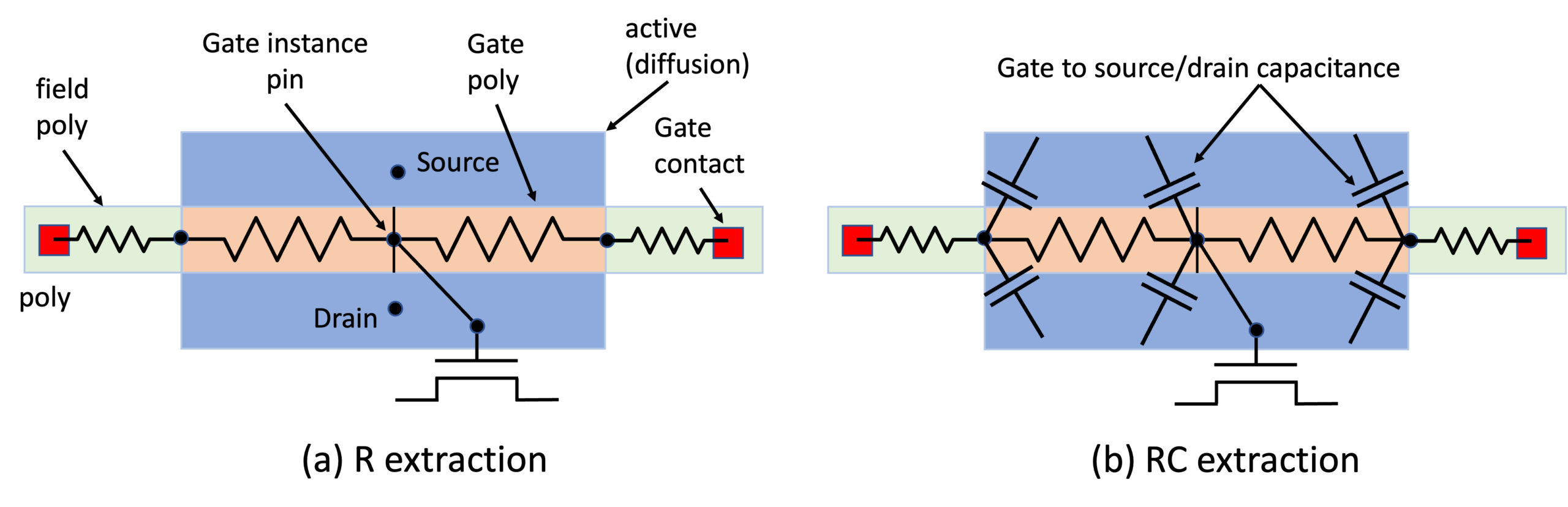

Tous les outils d'extraction parasites standard de l'industrie gèrent la résistance de grille et son extraction de la même manière. En configuration, la structure de grille MOS est représentée par un masque 2D traditionnellement appelé "poly" - même si le matériau peut être formé par un empilement métallique de grille complexe et peut avoir une structure 3D complexe.

Ils fracturent la ligne poly à l'intersection avec la couche active (diffusion), la divisant en "gate poly" (poly over active) et "field poly" (poly outside active), comme le montre la figure 3.

Gate poly est également fracturé au point central. La broche d'instance de porte du MOSFET (modèle SPICE) est connectée au point central du poly de porte. La grille poly est décrite par deux résistances parasites, reliant les points de fracture. Un modèle plus précis du gate poly, avec deux résistances positives et une résistance négative, peut être activé dans le PDK, mais certaines fonderies préfèrent ne pas l'utiliser (voir la section suivante sur le modèle Gate Delta).

Des résistances parasites représentant le champ poly sont connectées aux contacts de grille ou à des couches MEOL (Middle-End-Of-Line) et encore à des couches métalliques supérieures.

La capacité parasite extrinsèque du MOSFET entre grille poly et source/drain diffusion et contacts est calculée par des outils d'extraction parasite, et affectée aux nœuds des réseaux résistifs. Différents outils d'extraction le font différemment - certains outils connectent ces capacités parasites au point central du poly de grille, tandis que d'autres outils les connectent aux extrémités des résistances poly de grille. Les détails de la connexion de la capacité parasite au réseau de résistances de grille peuvent avoir un impact important et significatif sur la réponse transitoire et CA, en particulier dans les nœuds avancés (16 nm et moins), où la résistance parasite de grille est énorme.

Ces détails peuvent être vus dans le fichier DSPF, mais ne sont généralement pas abordés dans la littérature ouverte ou dans la documentation PDK de la fonderie. L'inspection visuelle des fichiers texte DSPF est fastidieuse et nécessite une certaine expertise. Des outils EDA spécialisés (par exemple ParagonX [3]) peuvent être utilisés pour visualiser la connectivité des réseaux RC pour les netlists post-mise en page (DSPF, SPEF), les sonder (voir et inspecter les valeurs R et C), effectuer une analyse électrique et faire d'autres choses utiles. .

Modèle de porte delta

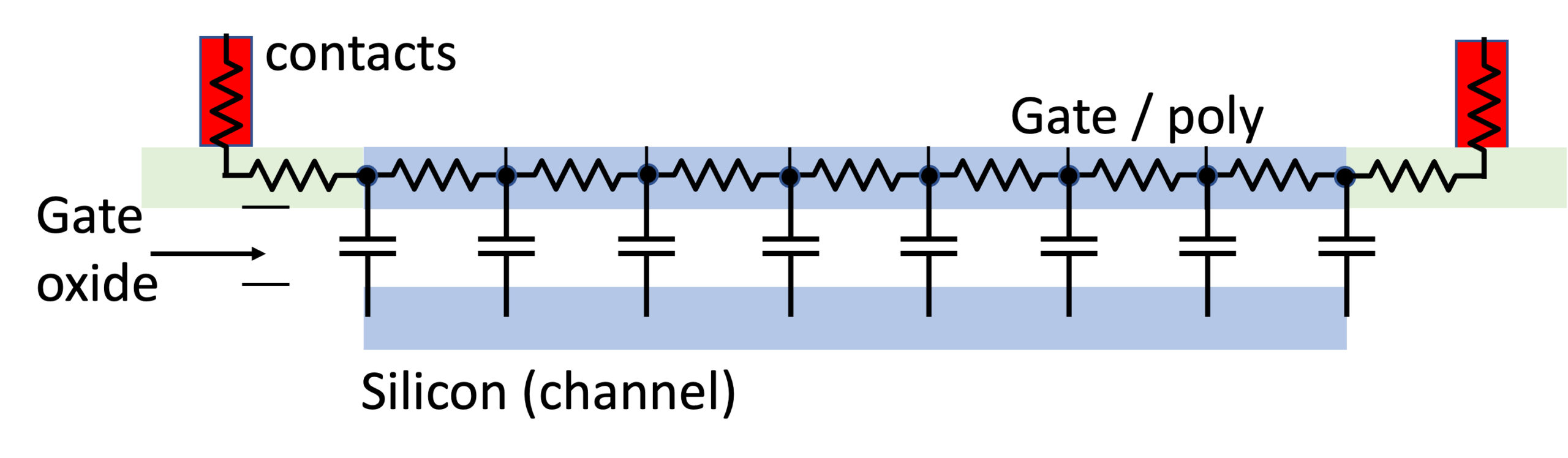

La porte MOSFET forme un grand réseau RC distribué le long de la largeur de la porte - illustré à la figure 4.

Ce réseau distribué a une réponse AC et transitoire différente de celle d'un simple circuit un-R et un-C. Il a été montré [2-3] qu'un tel réseau RC se comporte approximativement de la même manière qu'un réseau avec un élément R et un élément C, où C est la capacité totale, et R=1/3 * W/L *rsh pour un seul côté poly connecté, et R=1/12 * W/L * rsh pour poly connecté double face. Ces coefficients - 1/3 et 1/12 - permettent effectivement un modèle d'ordre réduit précis pour la porte, réduisant un grand nombre d'éléments R et C à deux (ou trois) résistances et un condensateur.

Pour activer ces coefficients dans une netlist RC standard (SPICE netlist ou DSPF), des gens intelligents ont inventé un soi-disant Gate Delta Model - où une porte est décrite par deux résistances positives et une négative - voir Figure 5.

Certains simulateurs SPICE ont des problèmes pour gérer les résistances négatives, c'est peut-être pourquoi ce modèle n'a pas été largement adopté. Certaines fonderies et PDK prennent en charge le modèle de porte delta, tandis que d'autres ne le font pas.

Beaucoup de gens sont surpris lorsqu'ils voient des résistances négatives dans les fichiers DSPF. Si ces résistances sont à côté de la broche d'instance de porte, elles font partie du circuit delta de porte.

Les effets distribués le long de la longueur de la grille (dans le sens de la source au drain) sont généralement ignorés au niveau de l'analyse du circuit, en raison d'une petite valeur de la longueur de la grille par rapport à la largeur de la grille.

Impact des parasites d'interconnexion sur la résistance de grille

Dans les « anciennes » technologies, les interconnexions métalliques (métaux et vias) avaient une très faible résistance, et la résistance de grille était dominée par la grille poly. L'analyse et le calcul de la résistance de grille étaient très simples.

Dans les technologies les plus récentes (par exemple, 16 nm et moins), les interconnexions ont une résistance très élevée et peuvent contribuer pour une part importante (50 % ou plus) à la résistance de grille. Selon la disposition, la résistance de grille peut avoir des contributions significatives de toutes les couches - dispositifs (porte poly, champ poly), MEOL ou BEOL.

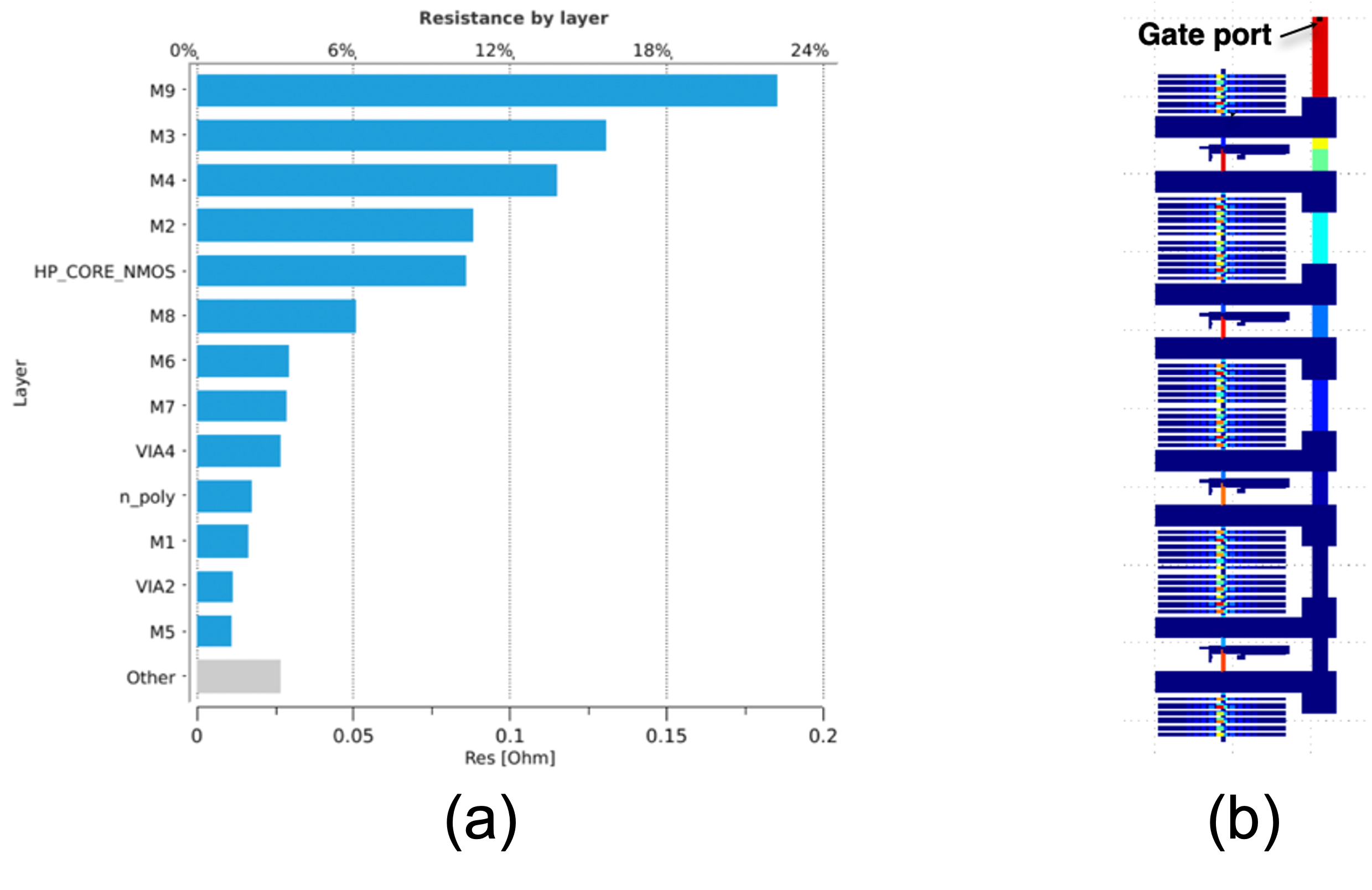

La figure 6 montre les résultats de la simulation de résistance de grille à l'aide de ParagonX [3]. Le diagramme de Pareto avec les contributions de résistance par couche permet d'identifier les couches les plus importantes pour la résistance de grille. La visualisation des contributions des polygones de mise en page à la résistance de grille indique immédiatement les points d'étranglement, les goulots d'étranglement pour la résistance de grille, ce qui est très utile pour guider les efforts d'optimisation de la mise en page.

Résistance de grille dans les FinFET

Dans les MOSFET planaires, la grille a une structure planaire très simple et le flux de courant dans la grille est unidimensionnel, dans le sens de la largeur de la grille.

Dans les technologies FinFET, la grille s'enroule autour d'ailettes en silicium très hautes et a donc une structure 3D très compliquée. De plus, le matériau de grille est sélectionné en fonction de la fonction de travail, pour régler la tension de seuil (la tension de seuil dans les FinFET n'est pas réglée par le dopage du canal, mais par les matériaux de grille). Ces matériaux ont une résistance très élevée, beaucoup plus élevée que le poly sollicité (qui a une résistivité de feuille typique d'environ 10 Ohm/sq). La grille peut être formée de plusieurs couches - couche d'interface avec le silicium et une ou plusieurs couches au-dessus.

Cependant, tous ces détails sont extraits des concepteurs de circuits intégrés et des ingénieurs de mise en page, et ils voient les polygones habituels pour "poly" et pour "actif" - ce qui facilite grandement le travail de conception.

Poignée de main entre le modèle SPICE et l'extraction parasite

En général, les modèles SPICE et les outils d'extraction parasite tiennent compte de la résistance de grille. L'extraction parasite est considérée comme une méthode plus précise de calcul des valeurs R et C parasites autour des appareils, car elle "connaît" (contrairement à SPICE) la disposition.

Pour éviter le double comptage de la résistance et de la capacité parasites (dans le modèle SPICE et dans l'extraction parasite), il existe un mécanisme de poignée de main entre la modélisation SPICE et l'extraction parasite, basé sur des paramètres d'instance spéciale.

Appareil standard vs modèles compacts RF Pcell

Les modèles MOSFET SPICE réguliers ne décrivent pas la résistance de grille avec suffisamment de précision pour les hautes fréquences, les vitesses de commutation élevées ou pour les performances RF ou de bruit. Pour permettre une haute précision de simulation, les fonderies recommandent généralement d'utiliser des cellules P RF, qui ont une taille fixe, qui contiennent un blindage (anneaux de garde et cages métalliques) et qui sont décrites par des modèles de haute précision dérivés des mesures. Cependant, ces cellules P RF ont une surface beaucoup plus grande que les MOSEFT standard, et de nombreux concepteurs préfèrent utiliser des MOSFET standard pour réduire la surface.

Composante verticale de la résistance de grille

Dans les « anciennes » technologies (avant 16 nm), la résistance de grille était dominée par la résistance latérale. Cependant, dans les technologies avancées, de multiples interfaces entre les couches de matériau de grille conduisent à une grande résistance de grille verticale. Cette résistance est inversement proportionnelle à la surface de la grille poly. Il peut être modélisé comme une résistance supplémentaire reliant la broche d'instance de porte au point central du poly de porte - voir la figure 7 (a). En conséquence, lorsque la grille devient plus étroite (plus petit nombre d'ailettes), la résistance de grille diminue, mais augmente à de très petites largeurs de grille. Il affiche un comportement non monotone caractéristique, comme le montre la figure 7(b). L'ancienne règle empirique selon laquelle "la porte la plus étroite a une résistance de porte plus faible" ne fonctionne plus. Les concepteurs et les ingénieurs de configuration doivent sélectionner la largeur de grille optimale (non minimale) (nombre d'ailettes), afin de minimiser la résistance de la grille.

![Figure7 (a) Modèle de grille tenant compte de la résistance de grille verticale, et (b) résistance de grille mesurée et simulée en fonction du nombre d'ailettes (réf. [2]).](https://zephyrnet.com/wp-content/uploads/2023/05/gate-resistance-in-ic-design-flow-6.jpg)

Selon la technologie, le PDK et la fonderie, la résistance de grille verticale peut ou non être incluse dans l'extraction parasite. Il est très facile de vérifier cela dans le fichier DSPF - si la broche d'instance de porte est connectée directement au centre de la porte poly - la résistance verticale n'est pas prise en compte. S'il est connecté par une résistance positive au centre de la porte poly - cette résistance représente la résistance verticale de la porte.

Tendances technologiques

Avec la mise à l'échelle de la technologie, les résistances de grille et les résistances d'interconnexion augmentent considérablement - jusqu'à un ou deux ordres de grandeur. En conséquence, les détails de la disposition qui n'étaient pas importants pour la résistance de grille dans les nœuds plus anciens deviennent très importants dans les nœuds avancés.

Autres structures de type porte MOSFET

Alors que la discussion sur la résistance de grille dans cet article se concentre sur les MOSFET, les mêmes arguments et approches sont applicables à d'autres systèmes distribués contrôlés par la grille ou par des systèmes de type porte, tels que :

• IGBT (transistors bipolaires à grille isolée)

• Condensateurs de découplage

• Condensateurs MOS

• Varacteurs

• Condensateurs à tranchée profonde et autres condensateurs intégrés de type MIM

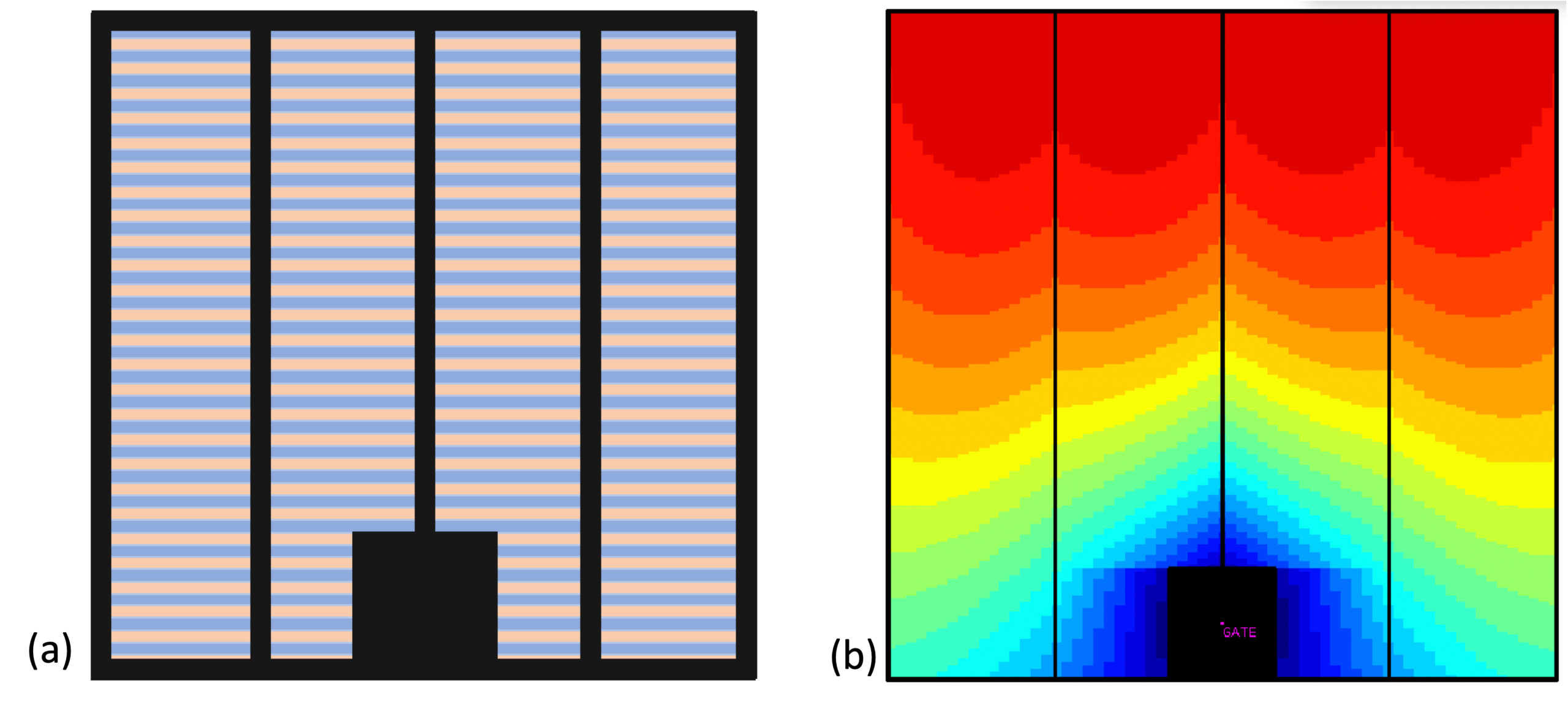

La figure 8 montre une structure de grille d'un MOSFET vertical et la distribution du retard de grille sur la zone de l'appareil, simulée à l'aide de ParagonX [3].

Bibliographie

1. B. Razavi, et al., "Impact de la résistance de grille distribuée sur les performances des dispositifs MOS", IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, vol. 41, pages 750-754, 11 1994.

2. AJSholten et al., "Modélisation compacte FinFET pour les applications analogiques et RF", IEDM'2010, p.190.

3. Guide de l'utilisateur ParagonX, Diakopto Inc., 2023.

Lisez aussi:

Analyse EM/IR rapide, une nouvelle catégorie EDA

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoAiStream. Intelligence des données Web3. Connaissance Amplifiée. Accéder ici.

- Frapper l'avenir avec Adryenn Ashley. Accéder ici.

- La source: https://semiwiki.com/eda/diakopto/328285-gate-resistance-in-ic-design-flow/