La demande incessante de SoC à faible consommation est évidente sur de nombreux marchés. Les exemples incluent les appareils mobiles, IoT et portables de pointe, ainsi que les demandes de calcul élevées pour les communications IA et 5G/6G. Les facteurs favorisant une faible consommation incluent la durée de vie de la batterie, la gestion thermique et, pour les applications de calcul intensif, le coût global de fonctionnement. Plusieurs approches sont disponibles pour obtenir une faible consommation. Un fil conducteur pour beaucoup est le besoin d’une IP Foundation optimale, c’est-à-dire de mémoires intégrées et de bibliothèques logiques. Il s’agit d’un domaine d’investissement important et de leadership sur le marché pour Synopsys. Deux publications informatives sont maintenant disponibles pour vous aider à comprendre les options et les avantages disponibles. Il s’avère qu’atteindre une consommation extrêmement faible avec les compilateurs de mémoire IP et les bibliothèques logiques de Synopsys Foundation est à portée de main.

Regardons les informations disponibles.

Bulletin technique

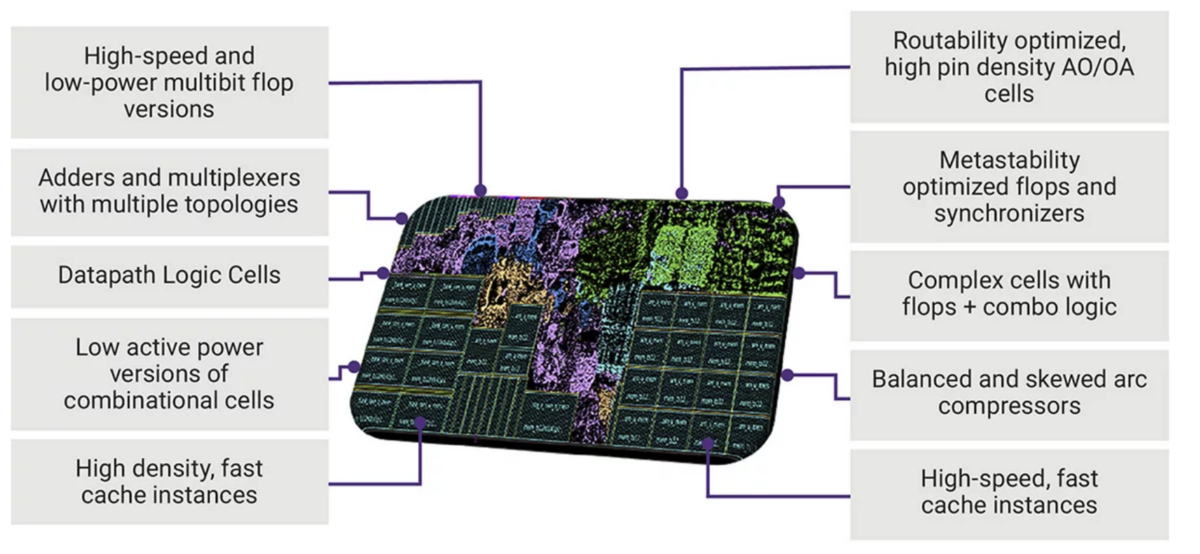

Je vais commencer par Optimisation du PPA pour les applications HPC et IA avec Synopsys Foundation IP, un bulletin technique axé sur les bibliothèques logiques. L'article fournit des détails sur la solution Foundation IP prenant en charge les outils de Synopsys. Des sujets tels que les circuits optimisés, la prise en charge d'une large plage de tensions de fonctionnement et la flexibilité d'ajouter des optimisations spécifiques au client sont abordés. L'article offre également une perspective sur l'obtention de performances maximales possibles ou du meilleur compromis puissance-performance. La figure ci-dessous résume les circuits de bibliothèque logique disponibles dans le kit de conception HPC.

Des détails sur la manière dont les améliorations de puissance sont obtenues sont fournis dans de nombreuses applications et stratégies de conception. Les sujets abordés incluent la mise à l'échelle dynamique de la tension sur une large plage de tension de fonctionnement, l'optimisation de l'IA et du bloc accélérateur spécifique à l'application PPA, les solutions pour le réseau sur puce et la manière dont le kit de conception Synopsys HPC est co-optimisé avec Synopsys EDA pour une mise en œuvre efficace du SoC.

Ce bulletin technique fournit un riche ensemble d’informations et d’exemples. Tu peux accéder à ces informations ici.

Publication

Un livre blanc complet intitulé : Jusqu’où pouvez-vous descendre ? Repousser les limites des transistors. Cette pièce explore à la fois les mémoires intégrées et les bibliothèques logiques. Il examine les détails permettant d’atteindre une puissance extrêmement faible. Plusieurs domaines d'application sont abordés, notamment le mobile, le Bluetooth et l'IoT, le calcul haute performance, l'automobile et la cryptographie.

Pour les mémoires embarquées, plusieurs approches sont discutées, notamment les techniques d'assistance et la division des tensions d'alimentation. Il est souligné qu’une co-optimisation minutieuse entre la technologie et la conception des circuits d’assistance à la mémoire est nécessaire pour assurer un fonctionnement de mémoire dense et à faible consommation à basse tension. Plusieurs techniques d'assistance améliorées sont passées en revue. Les améliorations de puissance vont de 10% à 37%.

La fiabilité des souvenirs est également discutée. L'article explique qu'à mesure que la tension diminue, la cellule SRAM commence à se dégrader. Cette dégradation peut entraîner de multiples problèmes : les lectures sont perturbées, la cellule binaire ne s'inverse pas, SER est prononcé, la détection échoue, les signaux de contrôle dévient et le signal BL s'affaiblit. Par conséquent, des techniques d’assistance sont nécessaires pour prendre en charge les tensions extrêmement basses requises par les applications de pointe à faible consommation.

Les approches adoptées par Synopsys ici font une différence significative. Des stratégies pour améliorer la fiabilité et des méthodes pour simuler le vieillissement sont discutées. Vous devriez lire les détails par vous-même – un lien arrive. Les données montrent des résultats convaincants, avec cinq à dix années de vie supplémentaires.

Les bibliothèques logiques sont également abordées, avec des stratégies permettant un fonctionnement à basse tension profonde à 0.4 V et moins. L'optimisation architecturale est également revue. Des techniques architecturales de cellule standard peuvent être utilisées pour réduire à la fois la puissance dynamique et la puissance de fuite. Par exemple, Synopsys utilise des techniques architecturales basées sur la pile plutôt que sur les étapes pour obtenir une topologie optimale pour un fonctionnement à basse tension profonde. La stratégie derrière cette approche est présentée.

L'optimisation de la caractérisation est également couverte. Un élément important de la caractérisation consiste à modéliser la variation du processus dans un SoC, appelée variation sur puce (OCV). Plusieurs techniques avancées sont utilisées ici, notamment l'apprentissage automatique pour augmenter la précision et optimiser les performances et la puissance.

Le livre blanc se termine par un aperçu de la façon de tout rassembler au niveau du SoC pour obtenir un fonctionnement à basse tension profonde. La réduction de tension est abordée, ainsi que les techniques de mise à l'échelle dynamique de tension et de fréquence (DVFS) et diverses stratégies d'arrêt telles que le sommeil léger, le sommeil profond, l'arrêt complet et les modes POFF (Périphérie OFF).

Ce livre blanc couvre un certain nombre de sujets d’optimisation de l’énergie de manière très détaillée. Je le recommande fortement. Tu peux obtenez votre copie ici. Et c'est ainsi qu'atteindre une consommation extrêmement faible avec les compilateurs de mémoire IP et les bibliothèques logiques de Synopsys Foundation est à portée de main.

Partagez cet article via:

- Contenu propulsé par le référencement et distribution de relations publiques. Soyez amplifié aujourd'hui.

- PlatoData.Network Ai générative verticale. Autonomisez-vous. Accéder ici.

- PlatoAiStream. Intelligence Web3. Connaissance Amplifiée. Accéder ici.

- PlatonESG. Carbone, Technologie propre, Énergie, Environnement, Solaire, La gestion des déchets. Accéder ici.

- PlatoHealth. Veille biotechnologique et essais cliniques. Accéder ici.

- La source: https://semiwiki.com/ip/341966-achieving-extreme-low-power-with-synopsys-foundation-ip-memory-compilers-and-logic-libraries/