Sen määrittäminen, onko 2.5D-laite painettu piirilevy, joka on kutistettu sopimaan pakkaukseen, vai siru, joka ulottuu yksittäisen muotin rajojen ulkopuolelle, saattaa tuntua hiuksia halkaisevalta semantiikalta, mutta sillä voi olla merkittäviä seurauksia kokonaismenestykseen. suunnittelusta.

Tasomaisia siruja on aina rajoittanut ristikon koko, joka on noin 858 mm2. Sen lisäksi tuottoongelmat tekevät piistä epätaloudellisen. Tämä on vuosien ajan rajoittanut tasomaiselle alustalle ahtautuvien ominaisuuksien määrää. Kaikki lisäominaisuudet on suunniteltava lisäsiruiksi ja yhdistettävä piirilevyyn (PCB).

Syntyminen 2.5D pakkaustekniikka on avannut kokonaan uuden akselin laajentumiselle, mikä mahdollistaa useiden sirut olla yhteydessä toisiinsa edistynyt paketti. Mutta tämän pakatun suunnittelun lähtöpisteellä voi olla suuri vaikutus siihen, miten eri komponentit kootaan, kuka on mukana ja mitä työkaluja käytetään ja milloin.

On useita syitä, miksi 2.5D yleistyy nykyään. Yksi on hinta. "Jos voit rakentaa pienempiä siruja tai siruja ja nuo sirut on suunniteltu ja optimoitu integroitaviksi pakkaukseen, se voi tehdä kokonaisuudesta pienemmän", sanoo Tony Mastroianni, kehittyneiden pakkausratkaisujen johtaja Siemens Digital Industries -ohjelmisto. "Ja koska tuotto on paljon korkeampi, sillä on dramaattinen vaikutus kustannuksiin. Sen sijaan, että stanssattujen lastujen tuotto olisi 50 % tai alle, voit nostaa sen jopa 90 %:iin."

Myös sirujen yhdistäminen piirilevyllä rajoittaa suorituskykyä. "Historiallisesti meillä oli siruja pakattu erikseen ja sitten asennettu piirilevylle ja kytketty yhteen reitityksellä", sanoo Ramin Farjadrad, Eliyanin toimitusjohtaja ja toinen perustaja. ”Ihmisten kohtaamat ongelmat olivat kaksijakoisia. Yksi oli, että näiden sirujen välistä kaistanleveyttä rajoitettiin käymällä läpi PCB ja sitten rajoitettu määrä palloja pakkauksessa, mikä rajoitti näiden sirujen välistä yhteyttä."

Keskeinen ero 2.5D:hen verrattuna piirilevyyn on se, että 2.5D käyttää sirun mittoja. Siellä on paljon hienojakoisempia lankoja, ja eri komponentit voidaan pakata paljon lähemmäksi toisiaan välilevylle tai pakkaukseen kuin levylle. Näistä syistä johdot voivat olla lyhyempiä, niitä voi olla enemmän ja kaistanleveys kasvaa.

Tämä vaikuttaa suorituskykyyn useilla tasoilla. "Koska ne ovat niin lähellä, sinulla ei ole pitkiä RC- tai LC-viiveitä, joten se on paljon nopeampi", sanoo Siemensin Mastroianni. ”Et tarvitse suuria kuljettajia sirulla ajaaksesi pitkiä jälkiä laudan yli, joten teho on pienempi. Saat suuruusluokkaa paremman suorituskyvyn – ja pienemmän tehon. Yleinen mittari on puhua pico jouleista bittiä kohden. Bittien siirtämiseen tarvittava energiamäärä tekee 2.5D:stä vakuuttavan."

Silti ajattelutapa vaikuttaa alkuperäiseen suunnittelukonseptiin, ja sillä on vaikutuksia koko kulkuun. "Jos puhut meistisuunnittelijan kanssa, he luultavasti sanovat, että se on vain iso siru", sanoo John Park, tuotehallintaryhmän johtaja Custom IC & PCB Groupista. kadenssi. "Mutta jos puhut pakkaussuunnittelijan tai levysuunnittelijan kanssa, he sanovat, että se on pohjimmiltaan pieni piirilevy."

Kuka on oikeassa? "Yrityksen sisäinen organisaatiorakenne päättää usein, miten tähän suhtaudutaan", sanoo Marc Swinnen, tuotemarkkinoinnin johtaja Ansys. "Pidemmällä aikavälillä haluat varmistaa, että yrityksesi on rakennettu vastaamaan fysiikkaa, etkä yritä vastata yrityksesi fysiikkaa."

Selvää on, että mikään ei ole varmaa. "Digitaalinen maailma oli hyvin säännöllinen siinä mielessä, että saimme kahden vuoden välein uuden puolet kokoisen solmun", Cadence's Park sanoo. ”Uusia vaatimuksia olisi, mutta se oli hyvin evolutiivista. Pakkaus on villi länsi. Saatamme saada 8 uutta pakkausteknologiaa tänä vuonna, 3 ensi vuonna ja 12 ensi vuonna. Monet näistä ovat peräisin valimoista, kun taas aiemmin vain ulkoistetuilta puolijohteiden kokoonpano- ja testausyrityksiltä (OSAT) ja substraattien toimittajilta. Vaikka valimot ovat uusi tulokas, OSATit tarjoavat todella mielenkiintoisia pakkaustekniikoita halvemmalla.

Osa syy tähän on se, että eri ihmisryhmillä on erilaiset vaatimukset. "Hallitus ja armeija näkevät ensisijaiset edut heterogeenisina integraatiokykyinä", Ansysin Swinnen sanoo. "He eivät työnnä prosessointiteknologian reunaa. Sen sijaan he suunnittelevat asioita, kuten monoliittisia mikroaaltointegroituja piirejä (MMIC), joissa he tarvitsevat aaltoputkia erittäin nopeille signaaleille. He lähestyvät sitä pakkauskokoonpanon näkökulmasta. Sitä vastoin korkean suorituskyvyn laskennan (HPC) yritykset lähestyvät sitä 5 nm:n ja 3 nm:n sirujen pinosta korkean suorituskyvyn korkean kaistanleveyden muistilla (HBM). He pitävät sitä piin kokoonpanoongelmana. He näkevät etuna arkkitehtuurin joustavuuden, jossa he voivat käyttää ytimiä ja rajapintoja ja luoda tuotteita tietyille markkinoille ilman, että jokaista sirua tarvitsee suunnitella uudelleen. He näkevät joustavuuden etuna. Armeija näkee heterogeenisen integraation etuna."

Tarvikkeet

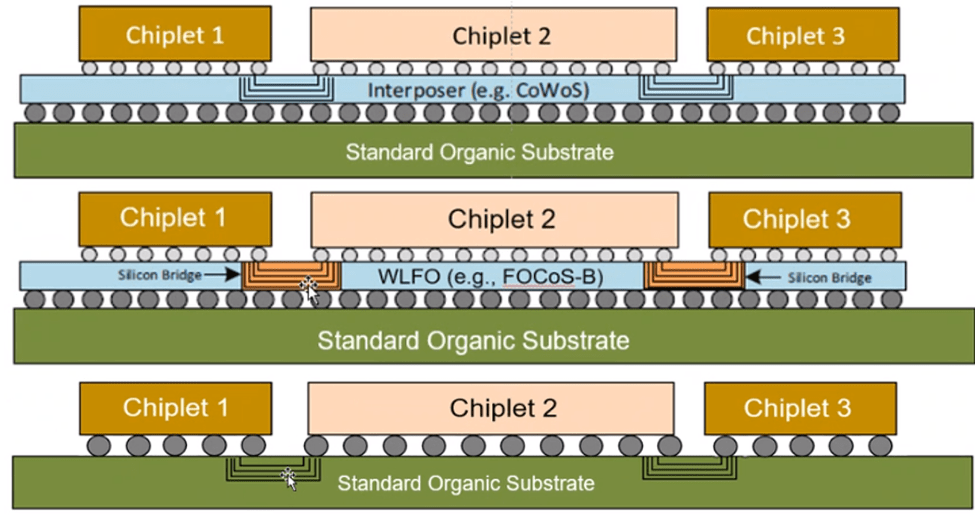

2.5D-pakkaustekniikassa käytetään alustana useita materiaaleja, joista jokaisella on erilainen kompromissi kustannusten, tiheyden ja kaistanleveyden suhteen, ja jokaisessa on erilaisia fyysisiä ongelmia, jotka on voitettava. Yksi tärkeimmistä erottelupisteistä on töyssyväli, kuten kuvassa 1 näkyy.

Kuva 1. Chiplet-liitäntä erilaisille substraattikokoonpanoille. Lähde: Eliyan

Kun puhutaan an välisovittimella, sitä pidetään yleensä piinä. "Välitys voi olla iso piipala (kuva 1 ylhäällä) tai vain piisilta sirujen välillä (kuva 1 keskellä) liitettävyyden takaamiseksi", Eliyanin Farjadrad sanoo. ”Molemmat näistä ratkaisuista käyttävät mikronystyjä, joiden tiheys on suuri. Interposerit ja sillat tarjoavat paljon tiheitä kuoppia ja jälkiä, mikä antaa sinulle kaistanleveyttä. Jos käytät 1,000 5 johtoa kukin 5 Gt:lla, saat 10,000 Tb. Jos sinulla on 50 1, saat 5 Tb. Mutta nuo signaalit eivät voi mennä kahta tai kolmea millimetriä pidemmälle. Vaihtoehtoisesti, jos vältät silikoniväliainepakkauksen ja pysyt orgaanisessa pakkauksessa (kuva 10 alaosa), kuten flip chip -pakkauksessa, jälkien tiheys on 5X - 10X pienempi. Johtojen paksuus voi kuitenkin olla 5X - 25X suurempi. Se on merkittävä etu, koska johtojen vastus pienenee johtimien paksuuden neliön verran. Tämän langan poikkileikkaus nousee tämän langan neliön verran, joten vastus laskee merkittävästi. Jos sen tiheys on XNUMXX pienempi, se tarkoittaa, että voit lähettää signaaleja lähes XNUMX kertaa pidemmälle."

Joillekin ihmisille kyse on kaistanleveydestä millimetriä kohti. "Jos sinulla on rinnakkaisväylä tai rinnakkaisliitäntä, joka on nopea ja haluat kaistanleveyttä millimetriä kohden, valitsisit todennäköisesti piivälityslaitteen", sanoo Kent Stahn, laitteistosuunnittelusta vastaava vanhempi johtaja. SynopsysRatkaisuryhmä. ”Orgaaninen substraatti on vähähäviöinen ja edullinen, mutta sillä ei ole tiheyttä. Niiden välissä on joukko ratkaisuja, jotka tarjoavat osan siitä, mutta eivät samalla hinnalla."

On myös muita syitä valita substraattimateriaali. "Piin väliaine tulee valimosta, joten saatavuus on ongelma", sanoo Manuel Mota, Synopsys' Solutions Groupin vanhempi henkilöstön tuotepäällikkö. ”Jotkut yritykset kohtaavat haasteita edistyneiden pakettien hankinnassa, koska kapasiteettia on varattu. Valitsemalla muut tekniikat, joilla on hieman pienempi kaistanleveystiheys, mutta ehkä tarpeeksi sovellukseesi, voit löytää ne muualta. Siitä on tulossa kriittinen näkökohta."

Kaikki nämä tekniikat kehittyvät kuitenkin nopeasti. "Riikkuraja on noin 858 neliömetriä", Park sanoo. ”Ihmiset puhuvat ehkä neljä kertaa suuremmista interposereista, mutta meillä on laminaatteja, jotka menevät paljon suurempia. Jotkut Japanista tulevista laminaattisubstraateista lähestyvät samaa yhteenliittämistiheyden tasoa, jonka voimme saada piistä. Itse näen enemmän ponnistuksia kohti orgaanisia substraatteja. TSMC:n Chip-on-Wafer-on-Substrate (CoWoS) käyttää piivälitysainetta, ja se on ollut valittu tekniikka noin 12 vuoden ajan. Äskettäin he esittelivät CoWoS-R:n, joka käyttää kalvopolyamidia lähempänä orgaanista substraattia. Nyt kuulemme paljon lasisubstraateista."

Ajan myötä paketin sisällä oleva kiinteistöjen kokonaismäärä voi kasvaa. "Ei ole järkevää, että valimot jatkavat 30 tuuman piirilevyn kokoisten esineiden rakentamista", Park lisää. ”On materiaaleja, jotka pystyvät käsittelemään suurempiakin malleja. Siellä, missä todella tarvitsemme tiheyttä, on kuolemasta kuolemaan. Haluamme nuo sirut vierekkäin, muutaman millimetrin pituudelta. Haluamme asiat hyvin lyhyinä. Mutta loput siitä vain tuulettavat I/O:ta, jotta se yhdistetään piirilevyyn."

Tästä syystä sillat ovat suosittuja. "Näemme etenemisen siltoihin rajapinnan nopeassa osassa", sanoo Synopsys' Stahn. "Sen takapuoli olisi fanout, kuten RDL fanout. Näemme jatkossa RDL-paketteja, jotka ovat enemmän perinteisten pakettien kaltaisia.

Interposerit tarjoavat lisäominaisuuksia. "Nykyään 99% väliinpitäjistä on passiivisia", Park sanoo. "Ei ole etupäätä, ei ole laitekerroksia. Se on puhtaasti takapään käsittelyä. Lisäät kolme, neljä, viisi metallikerrosta tuohon piihin. Sitä me kutsumme passiiviseksi välittäjäksi. Se vain luo sitä kuolla-kuolemaan välistä yhteyttä. Mutta on ihmisiä, jotka ottavat tuon kuopan ja tekevät siitä aktiivisen väliintulon, periaatteessa lisäämällä siihen logiikkaa."

Se voi tapahtua eri tarkoituksiin. "Näet jo joissakin yrityksissä aktiivisia interposoreita, joissa ne lisäävät virranhallintaa tai ohjauslogiikkaa", Mota sanoo. ”Kun alat laittaa aktiivisia piirejä interposerille, onko se edelleen 2.5D-integraatio vai muuttuuko siitä 3D-integraatio? Emme näe suurta suuntausta kohti aktiivisia välittäjiä nykyään."

Joitakin uusia ongelmia on kuitenkin. "Sinun on otettava huomioon lämpölaajenemiskertoimien (CTE) yhteensopimattomuus", Stahn sanoo. ”Tämä tapahtuu aina, kun kaksi materiaalia, joilla on eri CTE, liitetään yhteen. Aloitetaan piiväliaineesta. Voit saada suuremman tehon järjestelmiä, joissa SoC:t voivat puhua vertaistensa kanssa, ja se voi kuluttaa paljon virtaa. Silikoninen väliaine on silti mentävä pakkaukseen. CTE-epäsopivuus on piin ja pakkausmateriaalin välillä. Ja sillan kanssa käytät sitä siellä, missä sitä tarvitset, mutta silti se on silikonista kuoletta. Sinun on suoritettava lämpömekaaninen analyysi varmistaaksesi, että toimittamasi teho ja käytössäsi olevat CTE-epäsopimattomuudet johtavat toimivaan järjestelmään.

Vaikka signaalipituudet voivat teoriassa pidentyä, tämä aiheuttaa joitain ongelmia. "Kun teet noita pitkiä yhteyksiä sirun sisällä, rajoitat reitit yleensä muutamaan millimetriin ja puskuroit sen sitten", Mastroianni sanoo. "Passiivisen piivälityslaitteen ongelma on se, ettei siinä ole puskureita. Siitä voi todella tulla vakava ongelma. Jos sinun on tehtävä nämä yhteydet, sinun on suunniteltava ne erittäin huolellisesti. Ja sinun on varmistettava, että käytät ajoitusanalyysiä. Yleensä pakettikumppanisi eivät tee tätä analyysiä. Se on enemmän ongelma, joka on ratkaistu piiinsinöörien staattisen ajoitusanalyysin avulla. Meidän täytyy ottaa käyttöön STA-virtaus ja käsitellä kaikkia uutteita, jotka sisältävät orgaanisia ja piityyppisiä jälkiä, ja siitä tulee uusi ongelma. Kun alat päästä joihinkin noista hyvin pitkistä jäljistä, yksinkertaiset RC-ajoitusviiveesi, jotka oletetaan normaaleissa STA-viivelaskimissa, eivät ota huomioon osaa näiden jälkien välisestä induktanssista ja keskinäisestä induktanssista, joten voit saada vakavia tarkkuusongelmia. niille pitkille jälkille."

Aktiiviset välittäjät auttavat. "Aktiivisilla interposerilla voit voittaa joitakin pitkän matkan ongelmia asettamalla puskureita tai signaalitoistimia", Swinnen sanoo. ”Sitten se alkaa näyttää taas enemmän sirulta, ja sen voi tehdä vain piillä. Sinulla on Intelin EMIB-tekniikka, jossa he upotivat piirilevyn välilaitteeseen ja se on aktiivinen silta. Siru puhuu EMIB-sirun kanssa, ja he molemmat puhuvat sinulle tämän pienen aktiivisen siltapiirin kautta, joka ei ole varsinaisesti aktiivinen väliinpanija, mutta toimii melkein kuin aktiivinen välittäjä.

Mutta jopa passiiviset komponentit tuovat lisäarvoa. "Ensimmäinen asia, joka tehdään, on kaivantokondensaattoreiden sisällyttäminen välilaitteeseen", Mastroianni sanoo. "Tämä antaa sinulle mahdollisuuden tehdä hyvää irrottamista, missä sillä on merkitystä, lähellä stanssausta. Jos laitat ne pöydälle, menetät paljon nopeiden liitäntöjen eduista. Jos saat ne välilaitteeseen, joka istuu suoraan nopeasti vaihtavien nopeussignaalien alle, voit saada paikallisen irrotuksen."

Erilaisten materiaalien lisäksi on kysymys siitä, kuka suunnittelee välikappaleen. "Teollisuus näyttää pitävän sitä pienenä piirilevynä siinä yhteydessä, kuka suunnittelee", sanoo Matt Commens, Ansysin tuotehallinnan johtaja. ”Välittävät ovat yleensä pakkausinsinöörien suunnittelemia, vaikka ne ovatkin piiprosesseja. Tämä pätee erityisesti korkean suorituskyvyn tuotteisiin. Vaikuttaa epäintuitiiviselta, mutta heillä on signaalin eheyden tausta, he ovat suunnitelleet siirtolinjoja ja minimoineet yhteensopimattomuutta liitännöissä. Perinteinen IC-suunnittelija toimii komponenttinäkökulmasta. Niinpä ala varmasti kertoo meille, että ihmiset, jotka se on määrätty tekemään suunnittelutyötä, ovat pakkaustyyppisiä persoonia."

teho

Piirilevyjen ja välilevyjen reitityksessä on joitain huomattavia eroja. "Interposer-reititys on paljon helpompaa, koska komponenttien määrä on huomattavasti pienempi verrattuna piirilevyyn", sanoo Andy Heinig, tehokkaan elektroniikan osastopäällikkö. Fraunhofer IIS/EAS. ”Toisaalta välilaitteen sähköverkko on paljon monimutkaisempi johtuen metallikerrosten suuremmasta resistanssista ja siitä, että sähköverkko on katkaistu signaalijohdoilla. Die-to-die-rajapinnan reititys on monimutkaisempi reititystiheyden vuoksi.

Tehonsiirto näyttää hyvin erilaiselta. "Jos katsot piirilevyä, ne upottavat nämä suuret metalliset valualueet kerroksiin ja poistavat alueet, joissa asioiden täytyy mennä läpi", Park sanoo. "Laitit nippu kuparia ja sitten mitätöit muut. Emme voi rakentaa väliintuloa sillä tavalla. Meidän on talletettava liitäntä, joten pii-välityslaitteen teho- ja maarakenteet näyttävät enemmän digitaalisilta siruilta. Mutta signaali näyttää enemmän PCB- tai laminaattipakkaukselta.

Reititys näyttää enemmän PCB:ltä kuin sirulta. "Näet esimerkiksi kyynelpisaroita tai fileitä, joissa se muodostaa yhteyden tyynyyn tai läpivientiin parantaakseen satoa", Park lisää. "Nykyiset reititystyylit on kohdistettu enemmän piirilevyihin kuin digitaaliseen IC:hen, jossa on vain 90° kohtisuorat kulmat ja puhtaat reitityskanavat. Interposers, olipa kyseessä pii tai orgaaninen, läpivienti on usein suurempi kuin lanka, mikä on klassinen PCB-ongelma. Reitittimet, jos puhumme digitaalisista, ovat jälleen enemmän kuin pieni piirilevy kuin muotti."

TSV:t voivat myös aiheuttaa ongelmia. "Jos aiot pitää niitä neliöinä, menetät paljon tilaa kulmissa", Swinnen sanoo. "Haluat todella 45° näiden kohteiden ympärille. Piireitittimet ovat perinteisesti Manhattania, vaikka RDL-reitityksellä on ollut pitkä perinne, joka on ylin kerros, johon kohoumat yhdistetään. Siinä on perinteisesti käytetty kahdeksankulmaisia tai pyöreitä kohoumia ja sitten 45° reititystä. Se ei ole yhtä joustava kuin PCB-reititys, mutta heillä on uudelleenjakokerroksen reitittimiä, ja heillä on myös joitain reitittimiä, jotka tulevat täysin mukautetulta puolelta ja joissa on täysi jokireititys.

- SEO-pohjainen sisällön ja PR-jakelu. Vahvista jo tänään.

- PlatoData.Network Vertical Generatiivinen Ai. Vahvista itseäsi. Pääsy tästä.

- PlatoAiStream. Web3 Intelligence. Tietoa laajennettu. Pääsy tästä.

- PlatoESG. hiili, CleanTech, energia, ympäristö, Aurinko, Jätehuolto. Pääsy tästä.

- PlatonHealth. Biotekniikan ja kliinisten kokeiden älykkyys. Pääsy tästä.

- Lähde: https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/