Los procesadores configurables están de moda ahora, en gran parte gracias a RISC-V. Que es un ISA en lugar de un procesador, pero no pongamos objeciones. Brazo seguido con configurabilidad en Cortex-X. Ambos fueron precedidos considerablemente (un par de décadas) por las CPU Synopsys ARC® RISC y los DSP CEVA. Cada uno hizo hincapié en la capacidad de configuración como un diferenciador sobre otros procesadores integrados y han disfrutado de un éxito continuo al liderar con esa capacidad. Hace unos meses, Synopsys presentó una información útil sobre el por qué y el cómo de la configurabilidad, centrada naturalmente en los procesadores ARC.

¿Por qué configurar?

Hay varios conductores. Earbuds y, de manera más general, los dispositivos portátiles deben tener una potencia ultra baja con un procesamiento optimizado al máximo hasta el nivel de instrucción o por debajo de él. En la nube y la infraestructura de red, la computación se está desagregando para reducir las latencias y la energía. También exigiendo optimización para cumplir con esos objetivos. En los centros de datos, los servidores ahora descargan las búsquedas iniciales de la base de datos en SSD inteligentes, para la búsqueda y la predicción del desgaste. Las redes RAN abiertas distribuyen inteligencia y almacenamiento a través de la red para que sean rápidas y receptivas, pero deben ser muy rentables.

El soporte para la comunicación entre el automóvil y la infraestructura (V2X) es un ejemplo fascinante que vale un poco más historia de fondo. El Sistema de gestión de credenciales seguras (SCMS, por sus siglas en inglés) de EE. UU. es uno de los principales candidatos para la certificación V2X y se basa en una técnica de clave pública/privada denominada claves de mariposa unificadas. Esto permite que una segunda parte genere una secuencia de claves públicas para las cuales solo el creador conoce las claves privadas. Como era de esperar, este sistema hace mucho hincapié en el rendimiento. Hay operaciones de bucle en el proceso que impedirían alcanzar esos objetivos utilizando algoritmos de software convencionales que se ejecutan en un procesador. Estas secciones críticas para el rendimiento deben acelerarse de alguna manera.

Ampliación del procesador ISA

Parte de la razón por la que estos bucles son lentos es la sobrecarga en la canalización de la CPU para cada instrucción. Obtener, decodificar, enviar, especular, ejecutar, reescribir. Si una secuencia de instrucciones se puede comprimir en una o unas pocas instrucciones, eso puede ahorrar mucho tiempo al minimizar esta sobrecarga. También puede haber otras ventajas, como un procesamiento especial para la aritmética de palabras muy largas.

La tecnología Synopsys ARC APEX permite agregar instrucciones personalizadas para satisfacer esta necesidad. Un desarrollador construye (a través de APEX) Verilog para esas instrucciones. Esto puede conectarse a recursos de procesador estándar como códigos de condición, registros y señales. APEX insertará el Verilog en el núcleo ARC, esencialmente paralelo a la ALU. Cuando una instrucción se decodifica para esta operación especial, se dirigirá a la lógica personalizada en lugar de a la ALU. De lo contrario, el resto de la CPU y los flujos del compilador funcionan igual. Una manera fácil de plegar instrucciones personalizadas de forma nativa en el núcleo.

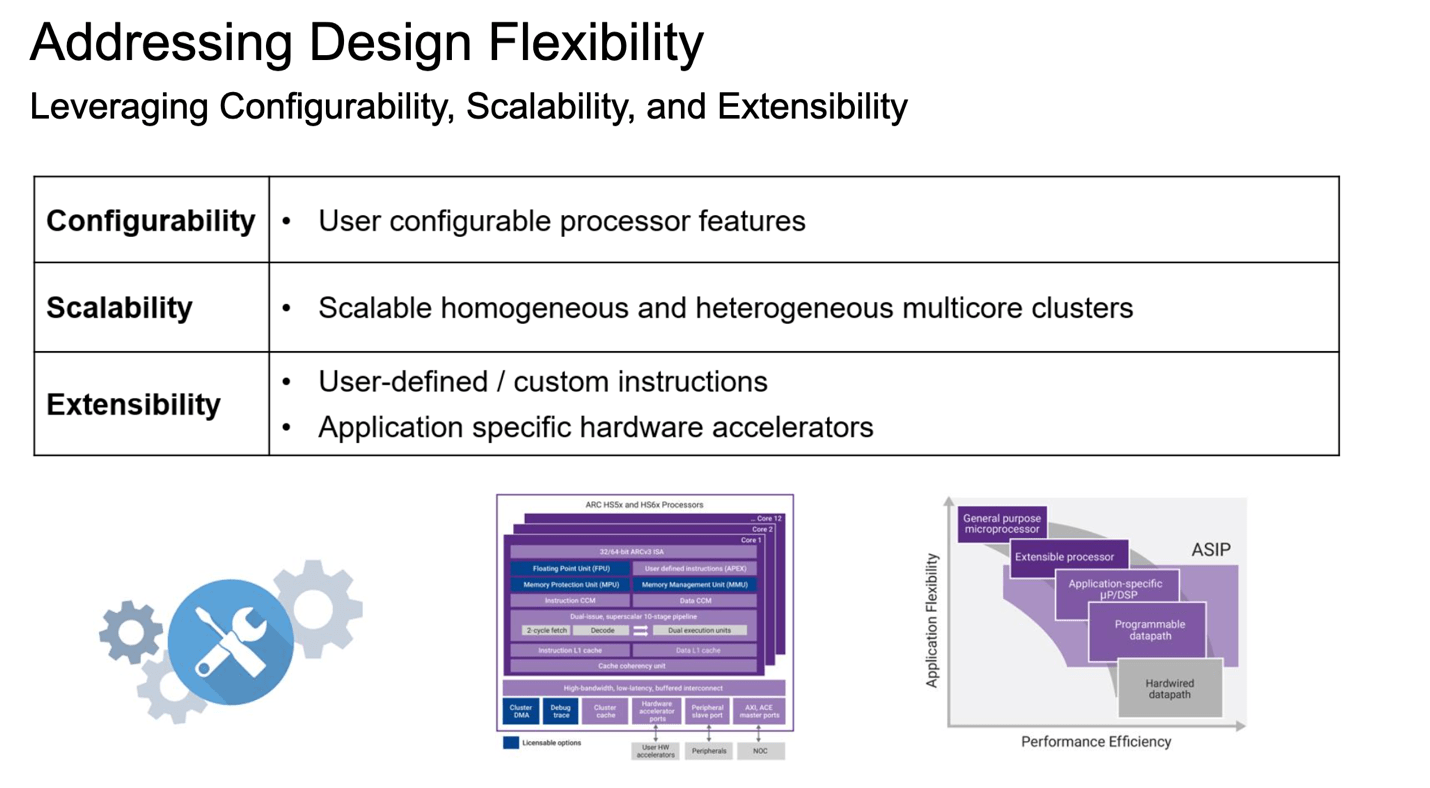

Debo agregar que Synopsys brinda otras opciones para la optimización: configurabilidad en el procesador central y paralelismo a través de implementaciones multinúcleo. También soporte para aceleradores de clientes estrechamente acoplados que pueden conectarse directamente a la caché compartida y compartir la memoria.

¿Vale la pena el esfuerzo?

Rich Collins (Director de marketing de productos) destacó un ejemplo en la charla: una optimización para un algoritmo de árbol rojo-negro (árboles de equilibrio) para una aplicación de almacenamiento. Aquí, los diseñadores pudieron reducir el tiempo de ejecución (y, en consecuencia, la energía) en un 50 % con poca área adicional. No tengo números para el diseño SCMS. (mencionado anteriormente en este artículo); estos son demasiado difíciles de desenredar de las mejoras de su algoritmo. Claramente, dependieron en gran medida de ARC y APEX para hacer factible su diseño.

Cosas interesantes. Puedes ver el webinar AQUÍ.

Comparte esta publicación a través de:

- Coinsmart. El mejor intercambio de Bitcoin y criptografía de Europa.Haga clic aquí

- Platoblockchain. Inteligencia del Metaverso Web3. Conocimiento amplificado. Accede Aquí.

- Fuente: https://semiwiki.com/automotive/320767-configurable-processors-the-why-and-how/