Κατά τη διάρκεια της GOMACTech συνέδριο που πραγματοποιήθηκε στη Νότια Καρολίνα την περασμένη εβδομάδα είχα μια κλήση Zoom με τον Deepak Shankar, ιδρυτή και αντιπρόεδρο τεχνολογίας στη Mirabilis Design Inc. για να κάνω ερωτήσεις και να δω μια ζωντανή επίδειξη του VisualSim – μια πλατφόρμα μοντελοποίησης, προσομοίωσης, εξερεύνησης και συνεργασίας για την ανάπτυξη ηλεκτρονικών και SoC. Αυτό που κάνει το VisualSim τόσο ξεχωριστό είναι ότι συνοδεύεται από περίπου 500 μπλοκ IP υψηλού επιπέδου έτοιμα προς χρήση, συμπεριλαμβανομένων 35 επεξεργαστών ARM, περίπου 100 επεξεργαστών και πάνω από 30 διαφορετικές διασυνδέσεις. Οι χρήστες του VisualSim συνδέουν γρήγορα αυτά τα μπλοκ IP μεταξύ τους οπτικά για να δημιουργήσουν τα συστήματά τους, συμπληρωμένα με δίκτυα. Ένας σχεδιαστής αυτοκινήτων μπορεί να μοντελοποιήσει ολόκληρο το δίκτυο, συμπεριλαμβανομένων των ενημερώσεων επικοινωνίας 5G, Ethernet, SDA και OTA με το VisualSim.

Ένα μοντέλο υψηλού επιπέδου επιτρέπει την ταχύτερη αρχιτεκτονική εξερεύνηση και την πραγματοποίηση αρχιτεκτονικών συμβιβασμών, πολύ πριν καν ξεκινήσει η εφαρμογή με τον κώδικα RTL. Μπορείτε να μοντελοποιήσετε σύνθετες δραστηριότητες όπως ένα λεωφορείο, μνήμες, ακόμη και προσωρινή μνήμη, μετρώντας πράγματα όπως καθυστερήσεις από άκρο σε άκρο και καθυστέρηση. Οι μηχανικοί μπορούν να μετρήσουν ποια είναι η αναλογία επιτυχίας/αστοχίας της κρυφής μνήμης και τι συμβαίνει με αιτήματα σε κρυφές μνήμες L2. Μοντελοποιούνται όλα τα δημοφιλή πρωτόκολλα δικτύου: AXI, CHI, CMN600, Arteris NOC, UCIe, κ.λπ.

Με αυτήν την προσέγγιση μοντελοποίησης ένας αρχιτέκτονας μπορεί να μοντελοποιήσει ένα SoC, ένα πλήρες σύστημα αεροσκαφών ή αυτοκινήτου και στη συνέχεια να αρχίσει να μετράει την απόδοσή του για να δει αν πληροί τις απαιτήσεις. Το VisualSim είναι ένας προσομοιωτής πολλών τομέων που μπορεί να ενσωματώσει αναλογικά, λογισμικό, συστήματα ισχύος, ψηφιακά και δικτύωση σε ένα ενιαίο μοντέλο.

Για τη ζωντανή επίδειξη, ο Deepak μου έδειξε ένα σχέδιο βασισμένο σε chiplet που είχε ξεχωριστά chiplet για το DSP, την GPU, τον επεξεργαστή AI και την CPU όλα συνδεδεμένα μεταξύ τους χρησιμοποιώντας UCIe και κάθε μπλοκ IP παραμετροποιήθηκε ώστε να επιτρέπει την προσαρμογή και την εξερεύνηση.

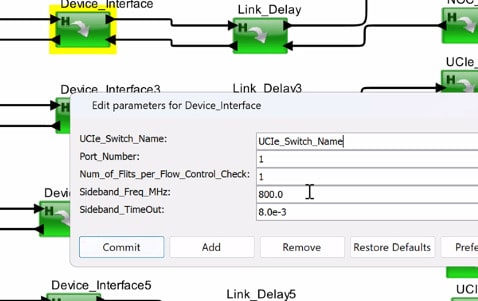

Πιέζοντας στο μπλοκ UCIe υπήρχε μια IP που ονομάζεται διακόπτης UCIe και ένας χρήστης μπορεί να προσαρμόσει αυτό το μπλοκ με πέντε παραμέτρους, όλες σε υψηλό επίπεδο.

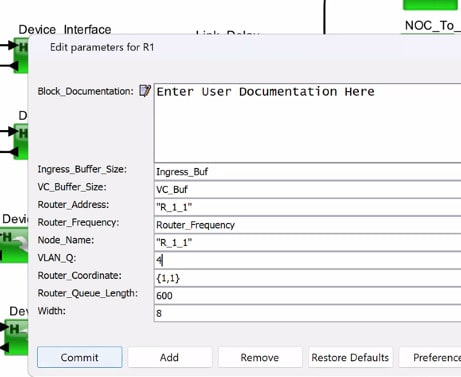

Ένα μπλοκ IP δρομολογητή είχε 10 παραμέτρους για προσαρμογή.

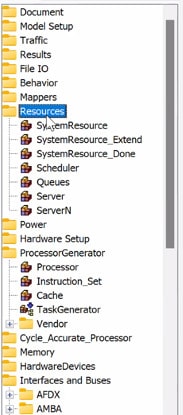

Για να βρείτε κάθε μπλοκ IP υπήρχε μια λίστα με δυνατότητα κύλισης στην αριστερή πλευρά του GUI, με κάθε οικογένεια IP στη βιβλιοθήκη. Σε λίγα δευτερόλεπτα μπορείτε να περιηγηθείτε, να επιλέξετε και να αρχίσετε να προσαρμόζετε μια IP.

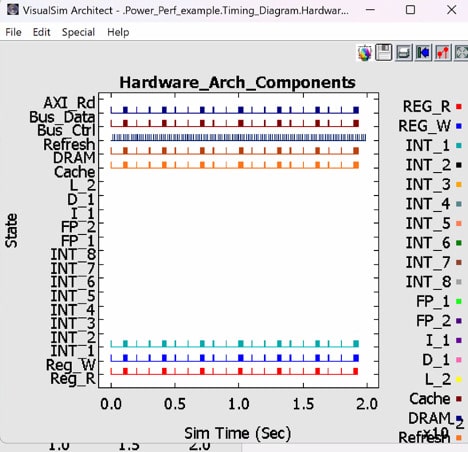

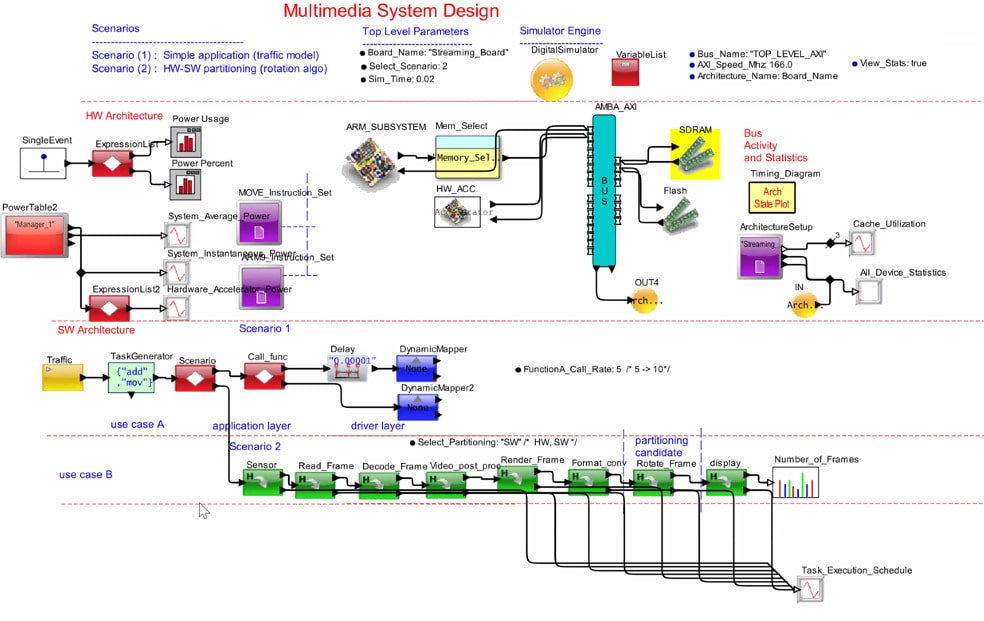

Στη VisualSim συνδέετε κάθε IP στη ροή δεδομένων, παραμένοντας σε υψηλό επίπεδο. Η επόμενη ζωντανή επίδειξη αφορούσε τη σχεδίαση συστήματος πολυμέσων και για την προσομοίωση 20 ms χρειάστηκαν περίπου 15 δευτερόλεπτα στον τοίχο, σε φορητό υπολογιστή. Ενώ εκτελείται η προσομοίωση, μπορείτε να δείτε την απόδοση του συστήματος ως στιγμιαία ισχύ, να μετρήσετε τη χρήση του αγωγού, τη χρήση της προσωρινής μνήμης, τη χρήση μνήμης και ακόμη και να προβάλετε ένα διάγραμμα χρονισμού. Αυτή η προσομοίωση σε πραγματικό χρόνο πυροδότησε 7.5 εκατομμύρια συμβάντα και ο πελάτης κατασκεύασε αυτό το μοντέλο σε λιγότερο από 2 εβδομάδες, το οποίο περιελάμβανε ολόκληρο το SoC.

Ένα άλλο παράδειγμα πελάτη που ανέφερε ο Deepak περιλαμβάνει 45 masters και ολοκληρώθηκε σε περίπου 4 εβδομάδες, πλήρως δοκιμασμένο.

Μπορείτε να κοιτάξετε μέσα σε οποιοδήποτε από τα μπλοκ IP και να αναλύσετε μετρήσεις όπως πέρασμα/αποτυχία και, στη συνέχεια, να καταλάβετε γιατί απέτυχε. Υπάρχει ακόμη και μια μηχανή τεχνητής νοημοσύνης που βοηθά στην πιο αποτελεσματική ανάλυση δεδομένων, όπως η εύρεση υπερχείλισης buffer που προκάλεσε αστοχία. Ενώ εκτελείται το μοντέλο σας, καταγράφονται αναλυτικά στοιχεία που βοηθούν στη μέτρηση της απόδοσης του συστήματος και στον εντοπισμό αρχιτεκτονικών σημείων συμφόρησης.

Το VisualSim ενημερώνεται δύο φορές το χρόνο και, στη συνέχεια, υπάρχουν ενημερώσεις ενημερώσεων κώδικα για όταν προστίθενται νέα μπλοκ IP. Ένας αρχιτέκτονας καθορίζει τις απαιτήσεις σε ένα αρχείο Excel, με μετρήσεις όπως τα όρια λανθάνοντος χρόνου και την κατάληψη buffer.

Οι χρήστες του VisualSim μπορούν να ορίσουν το εύρος του μεγέθους ωφέλιμου φορτίου σε byte, εύρη ταχύτητας και προτιμώμενες τιμές. Το μοντέλο του συστήματός σας μπορεί να σαρωθεί στους συνδυασμούς για να βρείτε το καλύτερο σύνολο παραμέτρων. Ο προσομοιωτής κατανοεί ακόμη και πώς να εξερευνήσει τις ελάχιστες, μέγιστες και προτιμώμενες τιμές. Μπορείτε να ορίσετε ποιες παράμετροι συστήματος θα διερευνηθούν. Στη συνέχεια προβλήθηκε μια επίδειξη συστήματος πολυμέσων και στη συνέχεια προσομοιώθηκε ζωντανά.

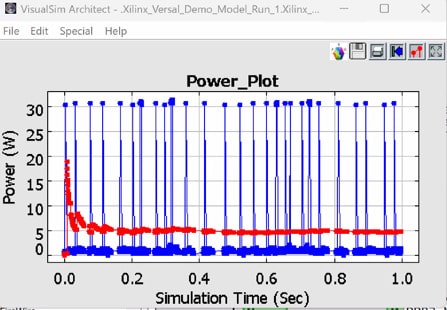

Για ένα μπλοκ FPGA επιλέγετε τον προμηθευτή και τον αριθμό εξαρτήματος και, στη συνέχεια, μπορείτε να δείτε τον λανθάνοντα χρόνο για κάθε Εργασία και τα στατιστικά του καναλιού του NOC μετά την εκτέλεση μιας προσομοίωσης. Εμφανίστηκε ένα διάγραμμα ισχύος για 1 δευτερόλεπτο λειτουργίας κατά τη χρήση εξαρτημάτων Xilinx Versal.

Όλες οι ζωντανές επιδείξεις εκτελούνταν σε φορητό υπολογιστή με Windows. Άλλα υποστηριζόμενα λειτουργικά συστήματα είναι: Unix, Mac. Η εκτέλεση του VisualSim απαιτεί μια ελάχιστη υποδομή HW, επειδή τα μοντέλα είναι υψηλού επιπέδου.

Οι χρήστες της VisualSim λαμβάνουν πάνω από 500 παραδείγματα που είναι προκατασκευασμένα για να σας βοηθήσουν να ξεκινήσετε γρήγορα, όπως ένα πλήρες σύστημα επικοινωνίας με κεραία, πομποδέκτη, FPGA με ζώνη βάσης και διασύνδεση Ethernet. Οι αρχιτέκτονες συστημάτων που χρησιμοποιούν VisualSim μπορούν να συνεργαστούν με όλους τους ειδικούς χαμηλού επιπέδου, όπως οι σχεδιαστές RTL.

Οι ανταλλαγές σε επίπεδο συστήματος μπορούν να μοντελοποιηθούν και να αξιολογηθούν, όπως:

- Αλλαγή από 64-QAM σε διαμόρφωση QPSK

- Ταχύτερος σε πιο αργός επεξεργαστής

- Αλλαγή προδιαγραφών Ethernet

Αν ξεκινήσετε με το VisualSim για να μοντελοποιήσετε, να εφαρμόσετε και μετά να μετρήσετε, περιμένετε να δείτε 95% ακρίβεια σε σύγκριση με τα αποτελέσματα υλοποίησης RTL. Η υπόσχεση χρήσης μοντέλων υψηλού επιπέδου είναι η εξάλειψη των προβλημάτων απόδοσης πριν από την υλοποίηση ή την ενσωμάτωση. Πραγματικά δεν απαιτείται κωδικοποίηση για ένα ολόκληρο μοντέλο συστήματος.

Η Mirabilis έχει μέχρι στιγμής 65 πελάτες παγκοσμίως και περίπου 250 έργα έχουν ολοκληρωθεί. Μερικοί από τους γνωστούς πελάτες περιλαμβάνουν: NASA, Samsung, Qualcomm, Broadcom, GM, Boeing, HP, Imagination, Raytheon, AMD, Northrup Grumman.

Χαρακτηριστικά

Παλιότερα, ένας σχεδιαστής συστημάτων μπορεί να σχεδίαζε τις ιδέες του σε μια χαρτοπετσέτα ενώ έτρωγε σε ένα εστιατόριο και μετά να επέστρεφε στη δουλειά και να συνδυάσει μερικά υπολογιστικά φύλλα του Excel με απόκρυφες εξισώσεις για να δημιουργήσει ένα μοντέλο. Σήμερα υπάρχει μια νέα επιλογή, και αυτή είναι η προσφορά VisualSim από τον Mirabilis μια δοκιμή. Τώρα μπορείτε να μοντελοποιήσετε ένα ολόκληρο σύστημα σε λίγες μόνο εβδομάδες, μαζί με την πραγματοποίηση αρχιτεκτονικών αντισταθμίσεων κατά την εκτέλεση πραγματικών προσομοιώσεων, όλα αυτά πριν ξεκινήσετε τις λεπτομερείς λεπτομέρειες υλοποίησης.

Σχετικά ιστολόγια

Μοιραστείτε αυτήν την ανάρτηση μέσω:

- SEO Powered Content & PR Distribution. Ενισχύστε σήμερα.

- PlatoData.Network Vertical Generative Ai. Ενδυναμώστε τον εαυτό σας. Πρόσβαση εδώ.

- PlatoAiStream. Web3 Intelligence. Ενισχύθηκε η γνώση. Πρόσβαση εδώ.

- PlatoESG. Ανθρακας, Cleantech, Ενέργεια, Περιβάλλον, Ηλιακός, Διαχείριση των αποβλήτων. Πρόσβαση εδώ.

- PlatoHealth. Ευφυΐα βιοτεχνολογίας και κλινικών δοκιμών. Πρόσβαση εδώ.

- πηγή: https://semiwiki.com/ip/343387-a-modeling-simulation-exploration-and-collaborative-platform-to-develop-electronics-and-socs/